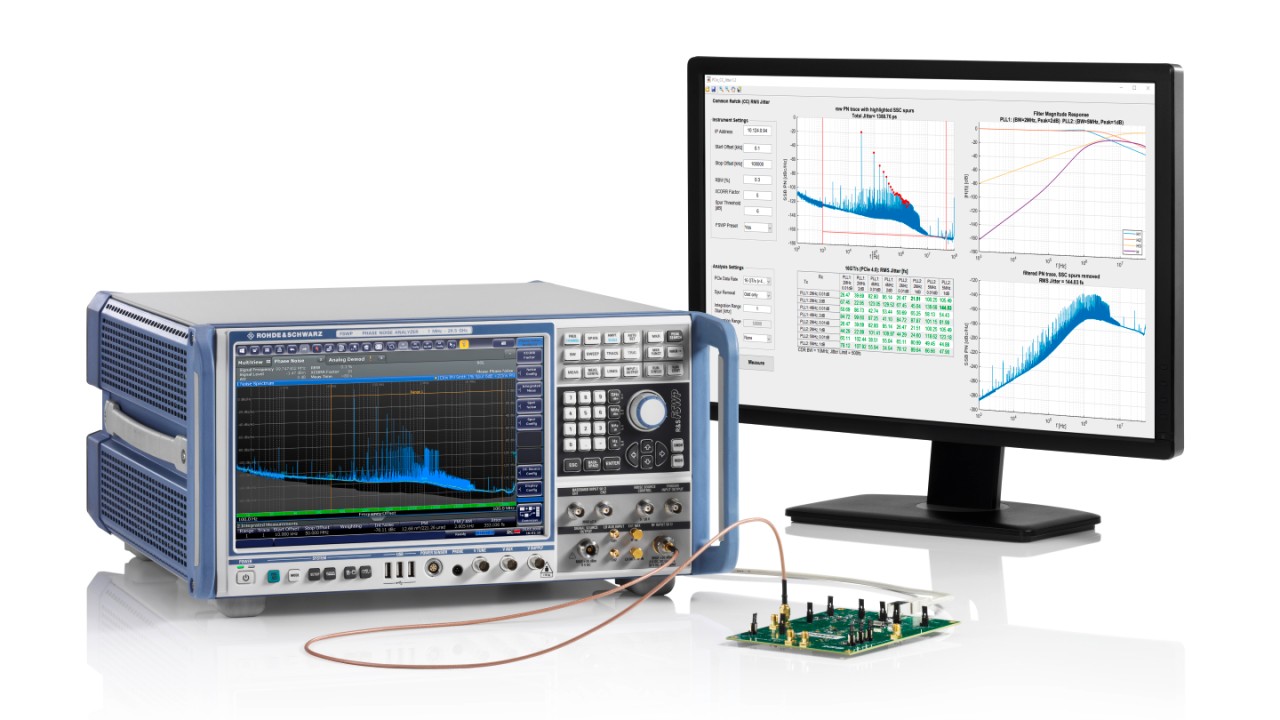

A solução da Rohde & Schwarz

A medição de jitter de clock geralmente consiste em:

- Medir o ruído de fase

- Ponderar o ruído de fase com base na função de transferência de sistema correspondente

- Integrar o ruído de fase ponderado na faixa definida de integração de jitter

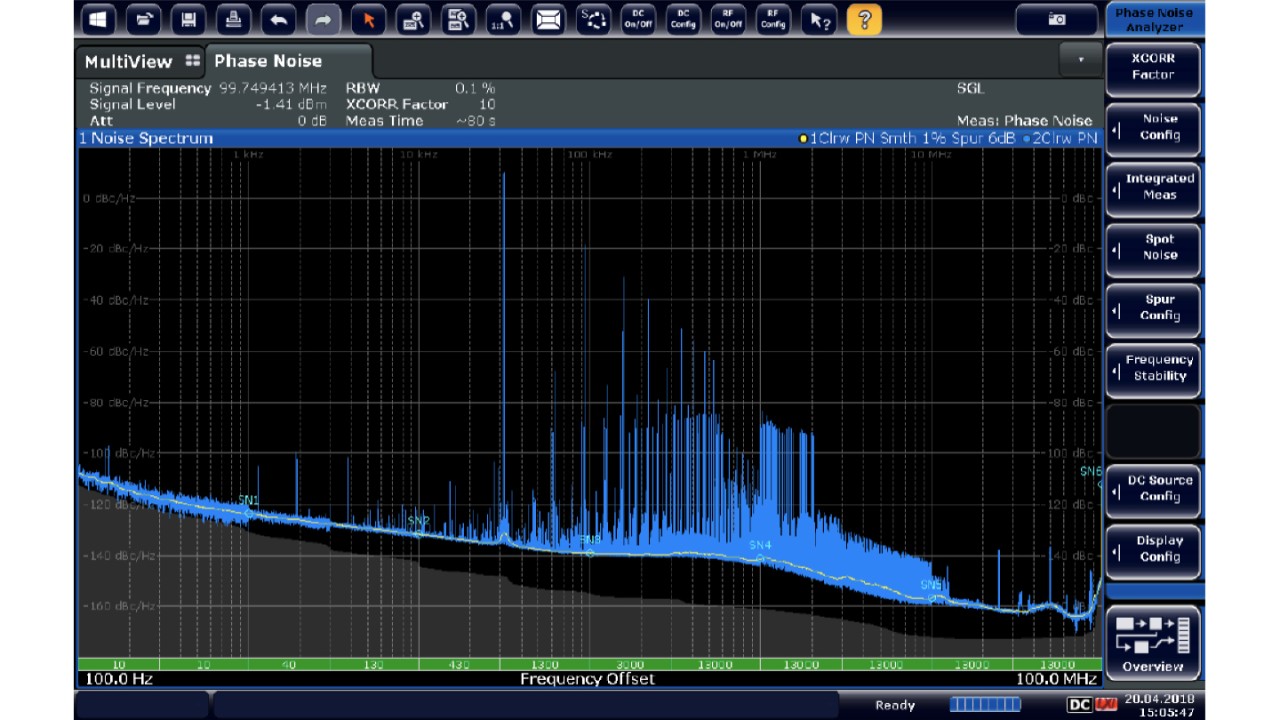

Medir o ruído de fase

No caso de clocks com uma taxa de variação alta, o jitter de clock é principalmente determinado pelo ruído de fase do clock. Como a velocidade de variação de saída do clock suprime o ruído da modulação em amplitude de forma considerável, ele normalmente não contribui para o jitter geral de clock. Para realizar medições precisas de jitter de clock, é importante uma supressão da modulação em amplitude alta na fase de medição de ruído.

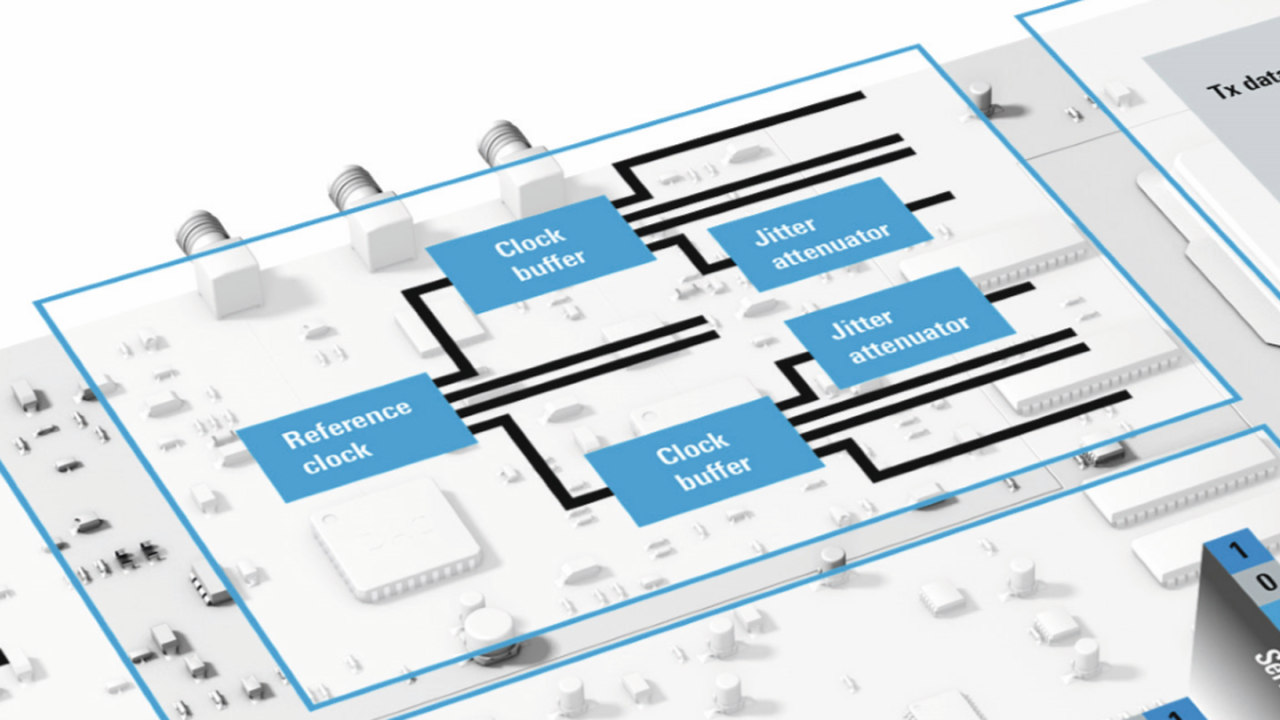

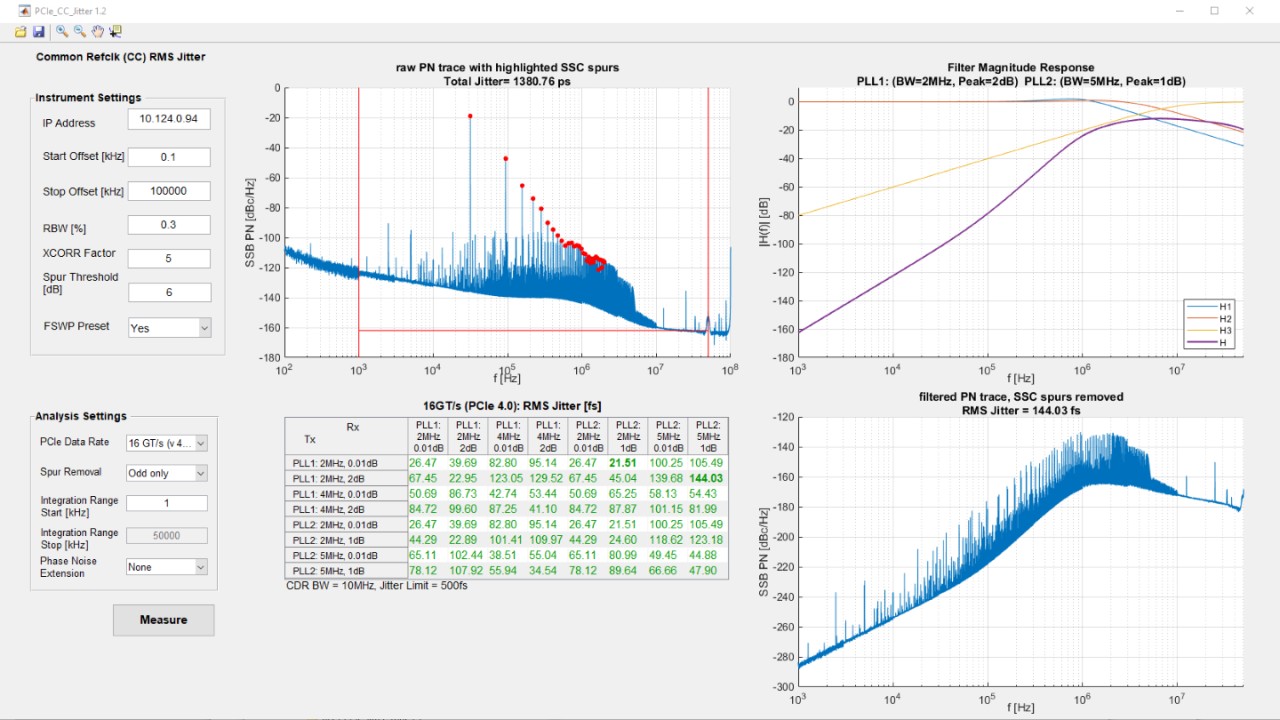

Ponderar o ruído de fase

Medições de jitter em tecnologias de alta velocidade, como PCIe, normalmente precisam incluir os efeitos de sistema das funções de transferência de anel de bloqueamento de fase de transmissor, anel de bloqueamento de fase de receptor e CDR. A função de transferência de sistema geral que resulta é aplicada ao traço de ruído de fase medido, como um filtro de ponderação, antes de integrar o jitter na faixa definida de integração de jitter.

Integrar o ruído de fase ponderado

O ruído de fase ponderado normalmente é integrado acima da frequência de Nyquist do clock (metade da taxa de clock) e, em alguns casos, ainda mais acima. Nesse caso, o ruído de fase também precisa ser medido acima dos offsets de frequências mais altas.