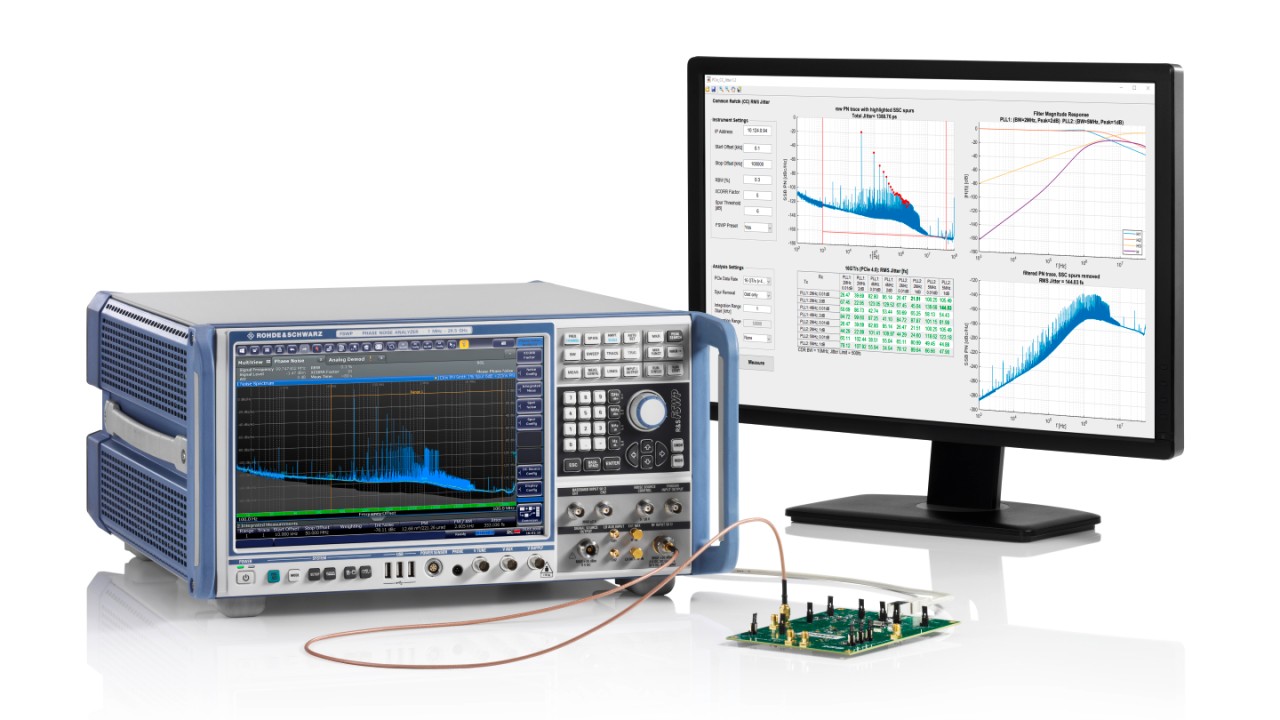

Lösung von Rohde & Schwarz

Jitter-Messungen an Taktsignalen beinhalten üblicherweise folgende Schritte:

- Messung des Phasenrauschens

- Gewichtung des Phasenrauschens mit den einzelnen Systemübertragungsfunktionen

- Integration des gewichteten Phasenrauschens über die definierte Jitter-Integrationsbandbreite

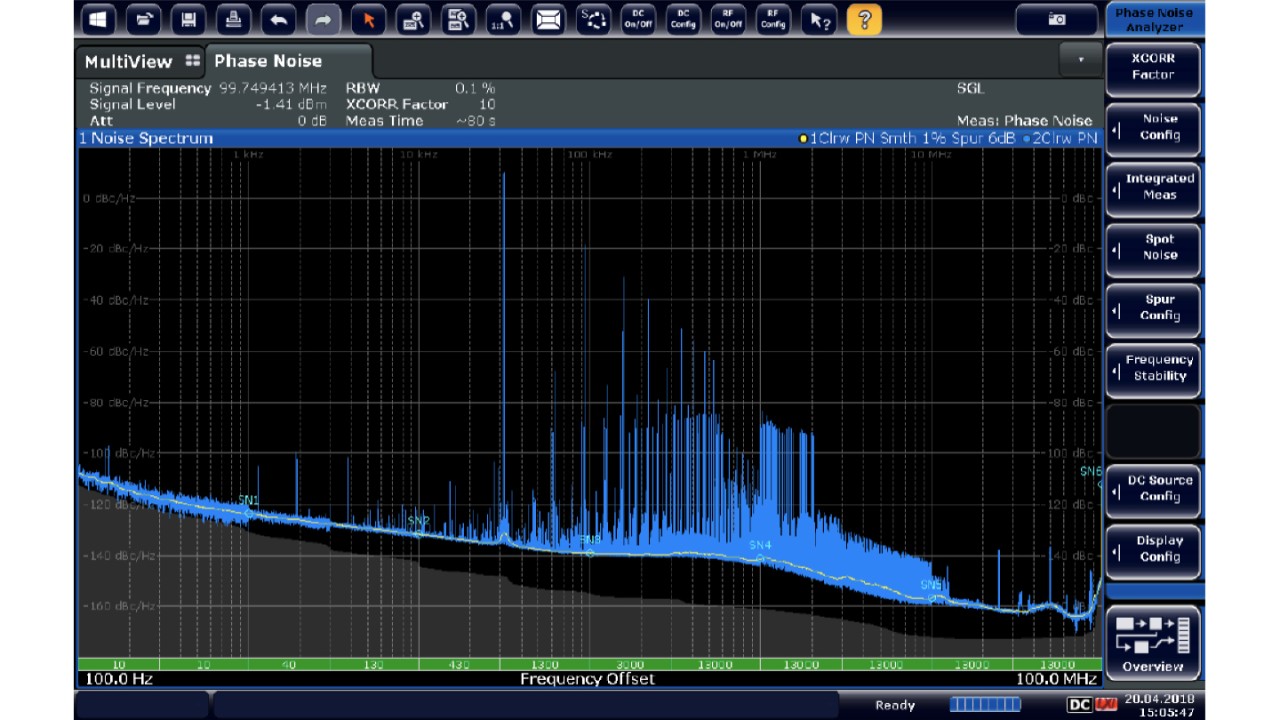

Messung des Phasenrauschens

Bei Taktsignalen mit hoher Flankensteilheit wird der Taktjitter hauptsächlich durch das Phasenrauschen des Taktsignals bestimmt. Da das AM-Rauschen durch die hohe Flankensteilheit des Taktsignals weitgehend unterdrückt wird, trägt es normalerweise nicht zum Gesamtjitter des Taktsignals bei. Für exakte Jitter-Messungen an Taktsignalen ist eine hohe AM-Unterdrückung bei der Phasenrauschmessung wichtig.

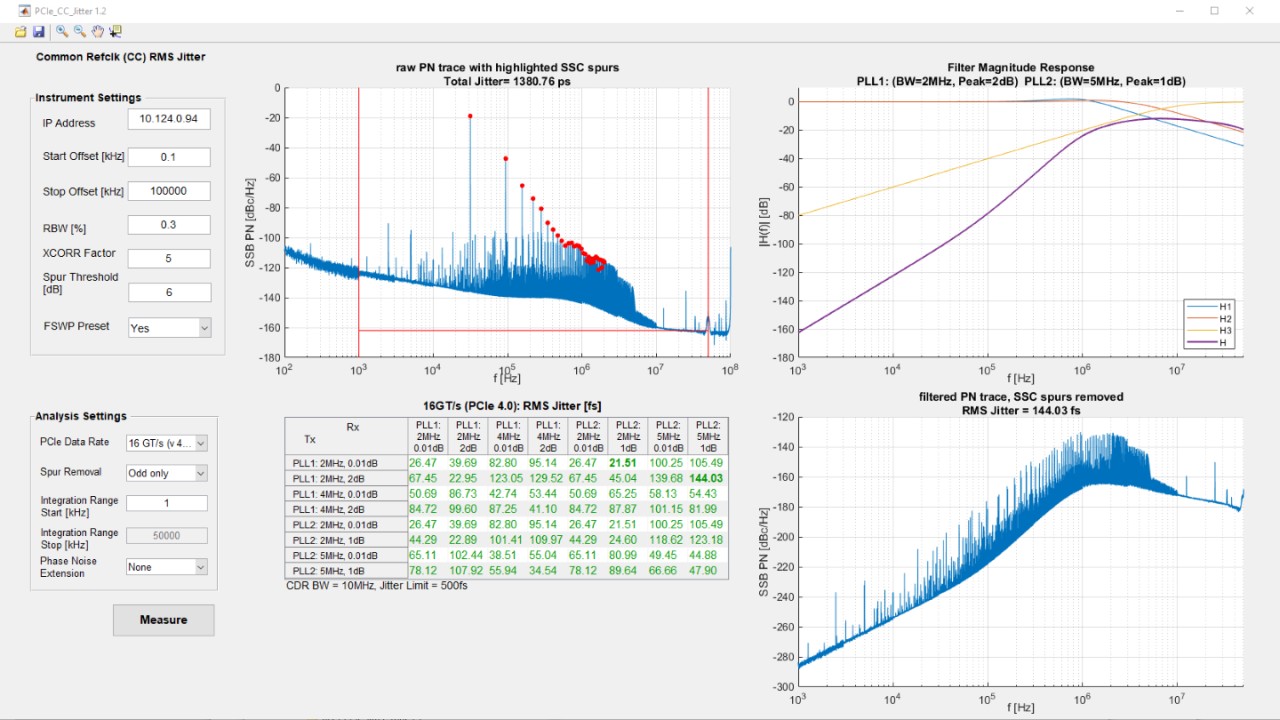

Gewichtung des Phasenrauschens

Jitter-Messungen bei Hochgeschwindigkeits-Technologien wie PCIe müssen üblicherweise die Auswirkung der Übertragungsfunktionen TX PLL, RX PLL und CDR (Clock Data Recovery, Taktdatenrückgewinnung) auf das System berücksichtigen. Die resultierende Übertragungsfunktion des Gesamtsystems wird auf die Phasenrausch-Messkurve als Gewichtungsfilter angewendet, bevor der Jitter über die definierte Jitter-Integrationsbandbreite integriert wird.

Integration des gewichteten Phasenrauschens

Das gewichtete Phasenrauschen wird üblicherweise bis zur Nyquist-Frequenz des Taktsignals (halbe Taktrate) integriert und in einigen Fällen sogar darüber. In diesen Fällen muss das Phasenrauschen auch bis zu höheren Frequenzoffsets gemessen werden.