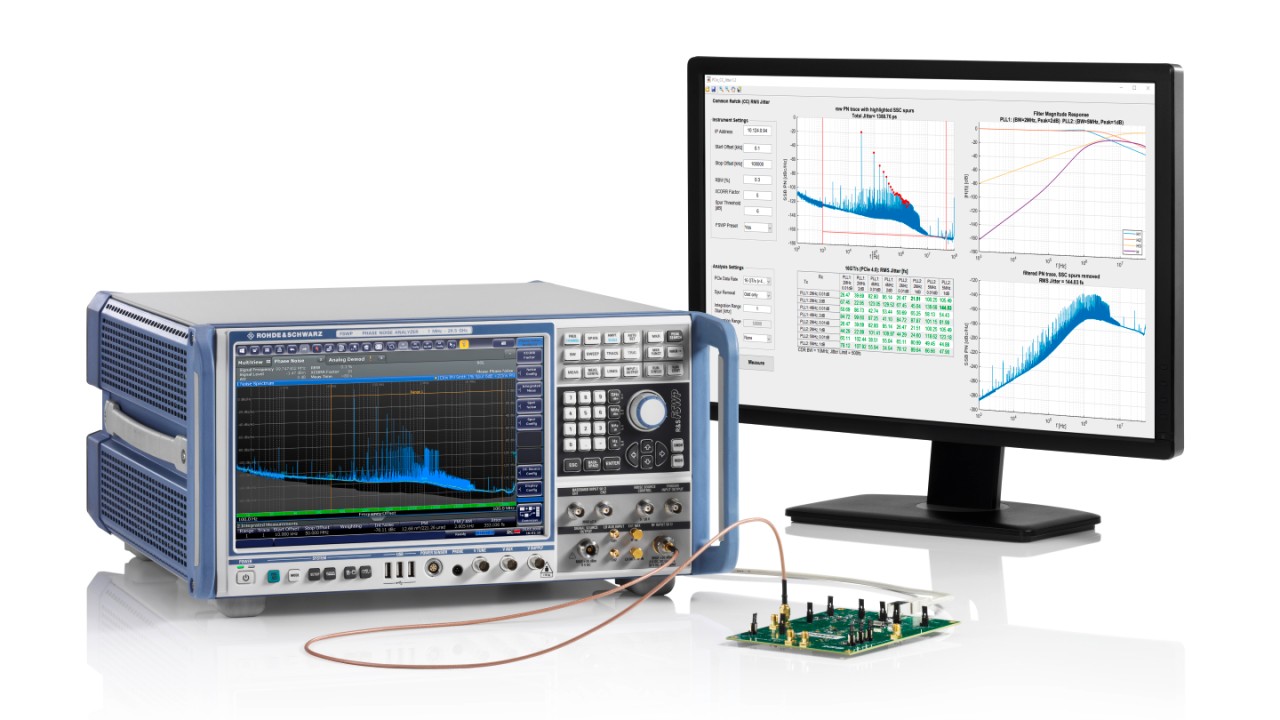

Solución Rohde & Schwarz

Las medidas de fluctuación de fase de reloj se dividen normalmente en varios pasos:

- Medida del ruido de fase

- Ponderación del ruido de fase basada en la función de transferencia correspondiente del sistema

- Integración del ruido de fase ponderado en el rango de integración de fluctuación de fase definido

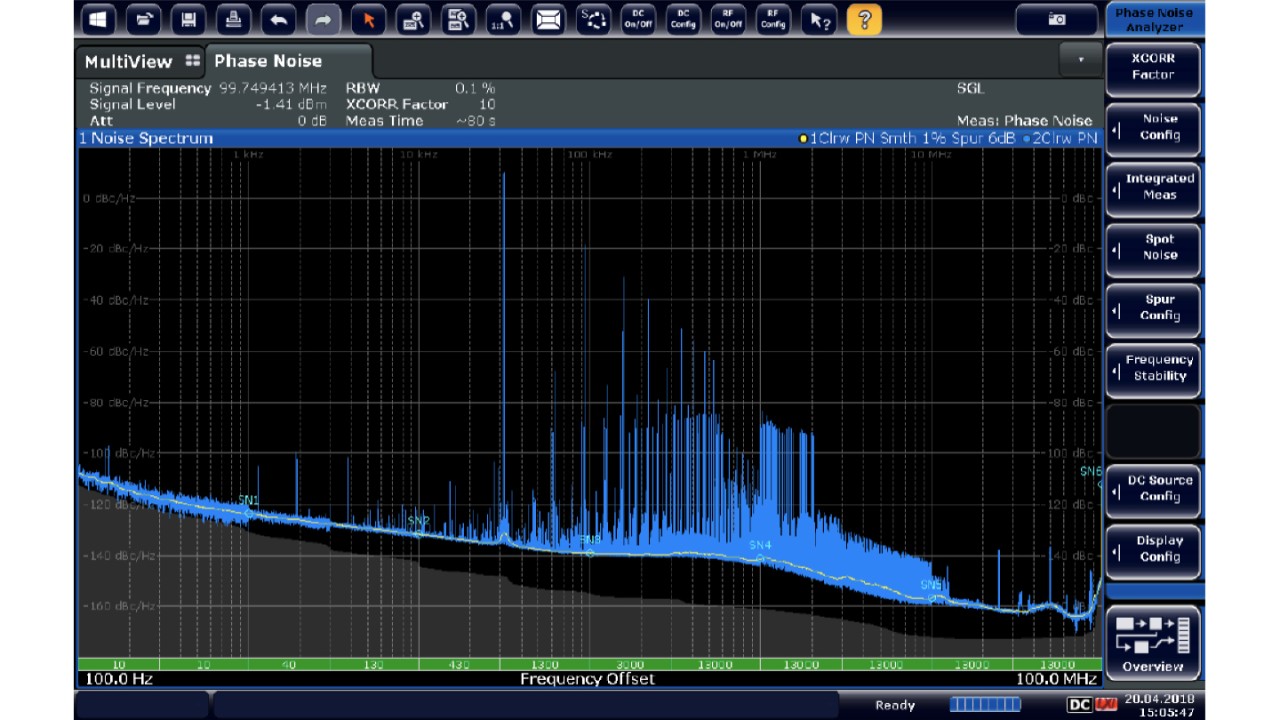

Medida del ruido de fase

En el caso de relojes con una alta rapidez de respuesta, la fluctuación de fase viene determinada principalmente por el ruido de fase del reloj. Como el ruido AM queda suprimido en gran medida por la elevada velocidad de respuesta del reloj, dicho ruido no contribuye generalmente a la fluctuación de fase total del reloj. Para conseguir medidas precisas de fluctuación de fase del reloj, es importante suprimir la modulación de amplitud (AM) al medir el ruido de fase.

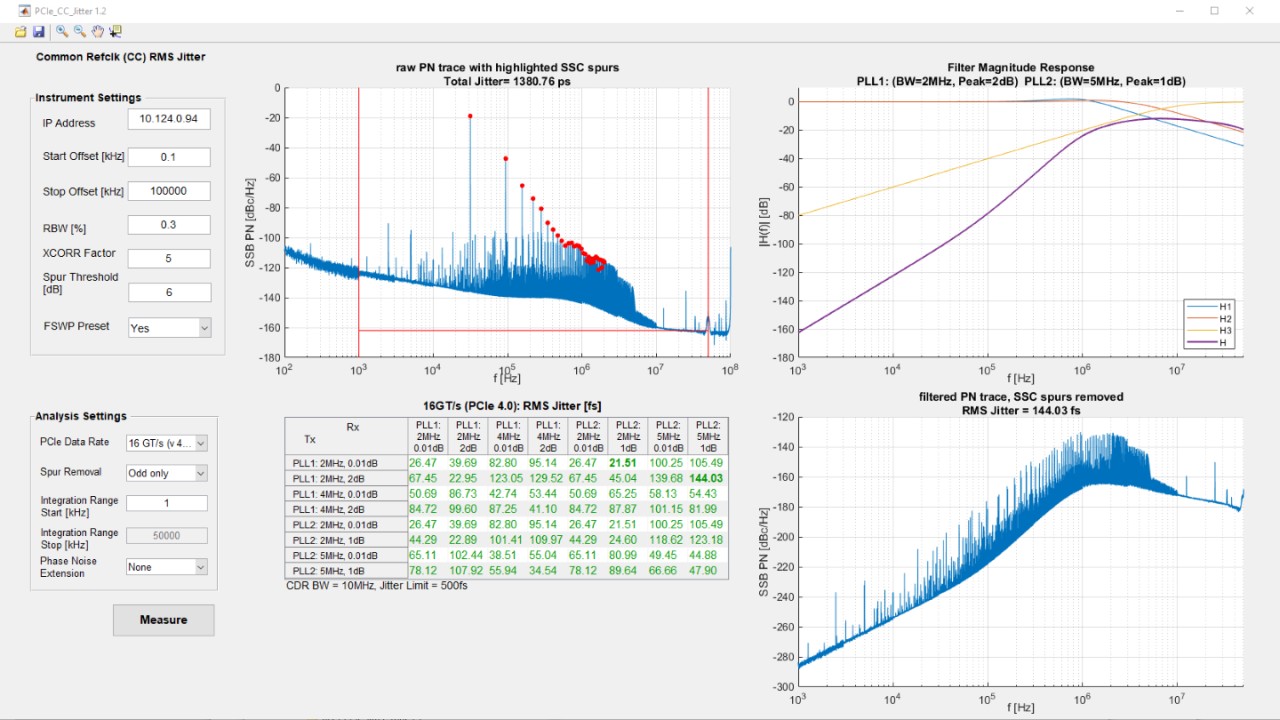

Ponderación del ruido de fase

Para medir la fluctuación de fase en tecnologías de alta velocidad como PCIe, es necesario por lo general incluir los efectos que tienen en el sistema las funciones de transferencia de TX PLL, RX PLL y CDR. La función de transferencia total resultante del sistema se aplica como filtro de ponderación a la traza de ruido de fase medida antes de integrar la fluctuación de fase en el rango definido.

Integración del ruido de fase ponderado

El ruido de fase ponderado se integra comúnmente hasta la frecuencia Nyquist del reloj (la mitad de la velocidad del reloj), y en ocasiones incluso por encima. En ese caso, el ruido de fase también debe medirse hasta desfases de frecuencia superiores.