Test efficienti con diagrammi a occhio dei sistemi di memoria DDR3/DDR4

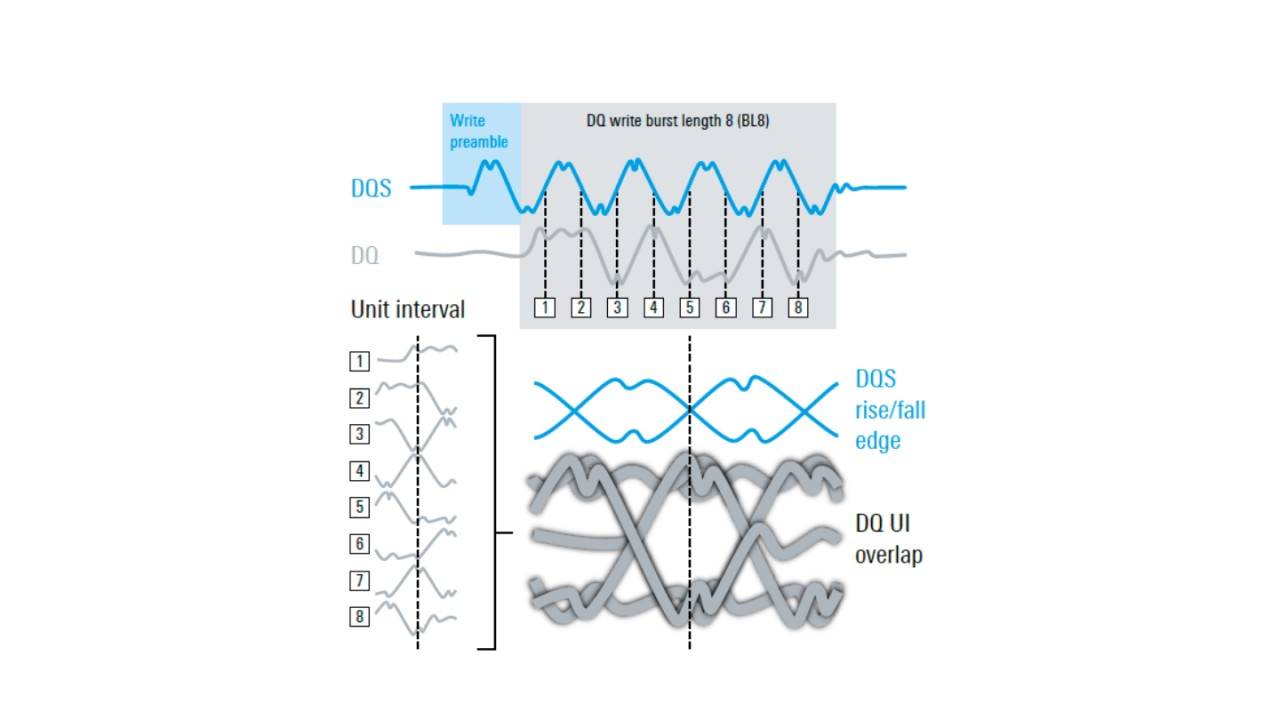

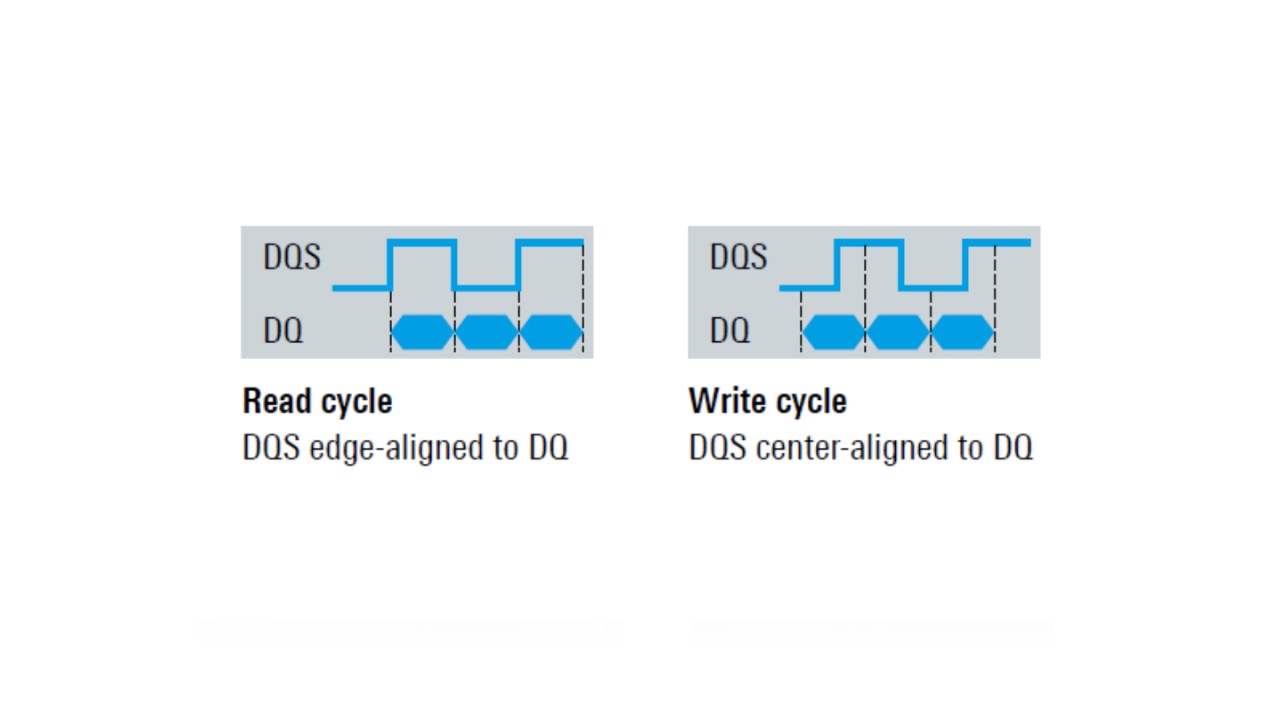

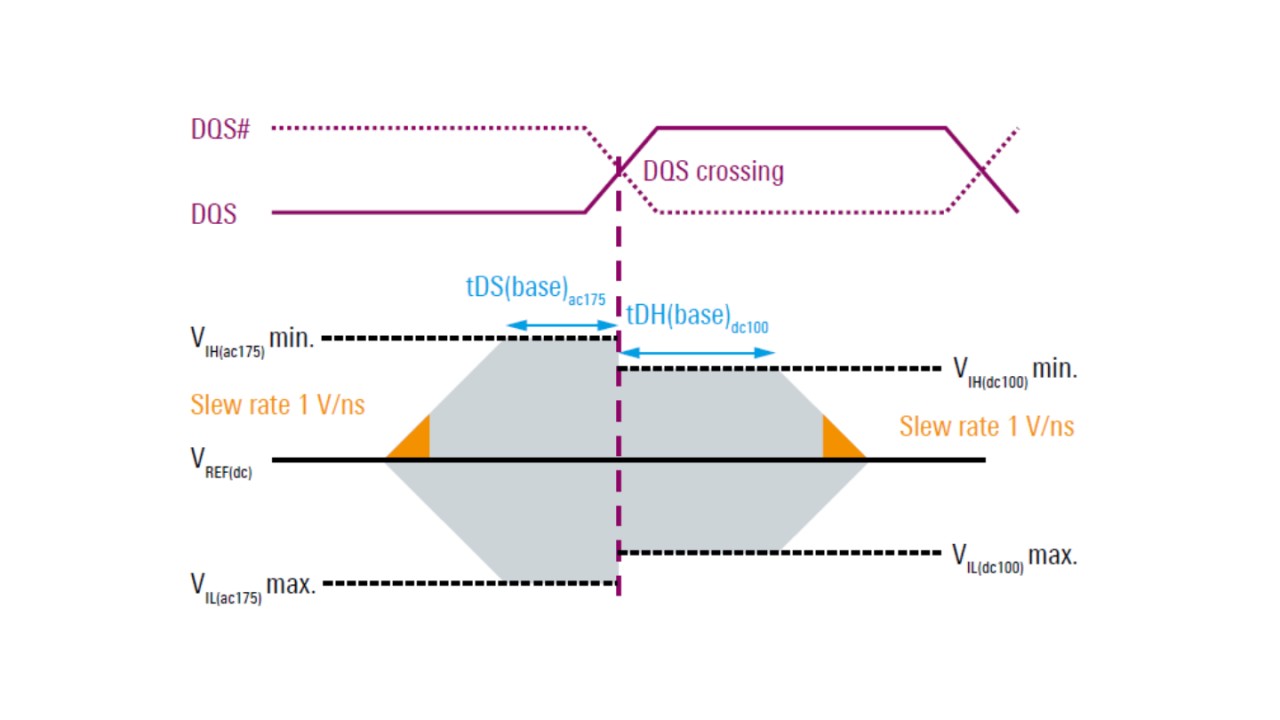

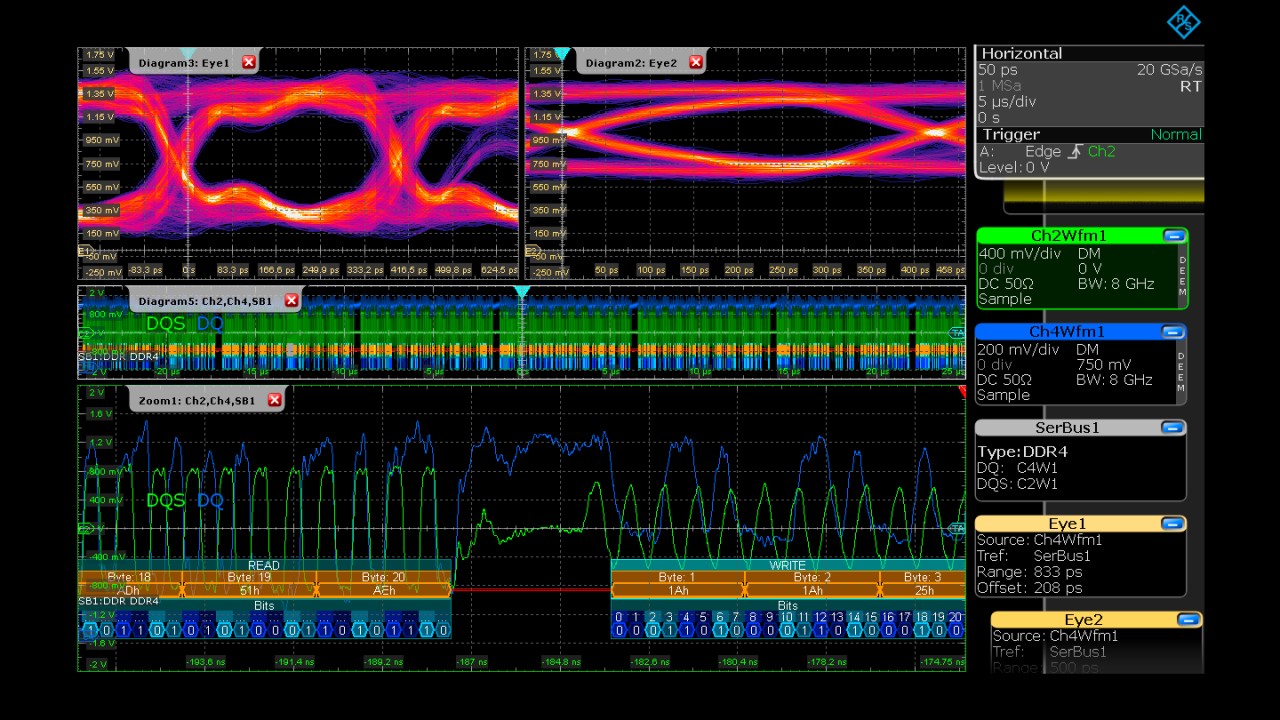

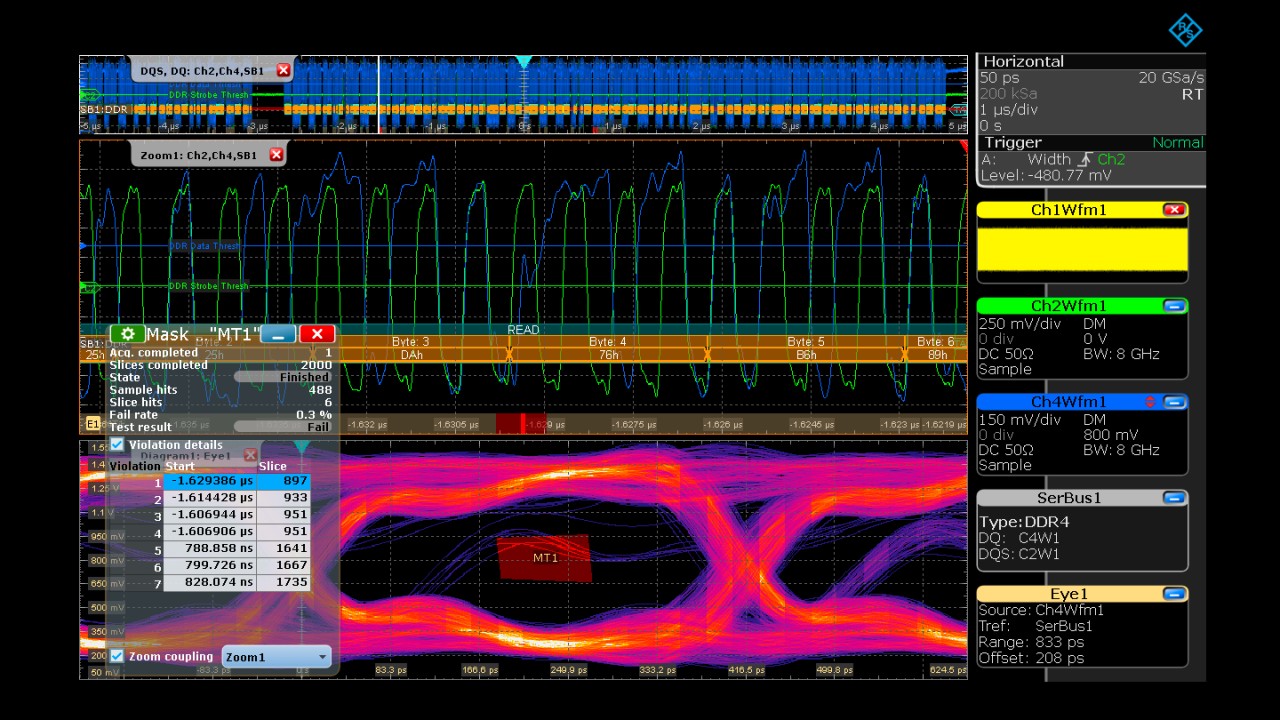

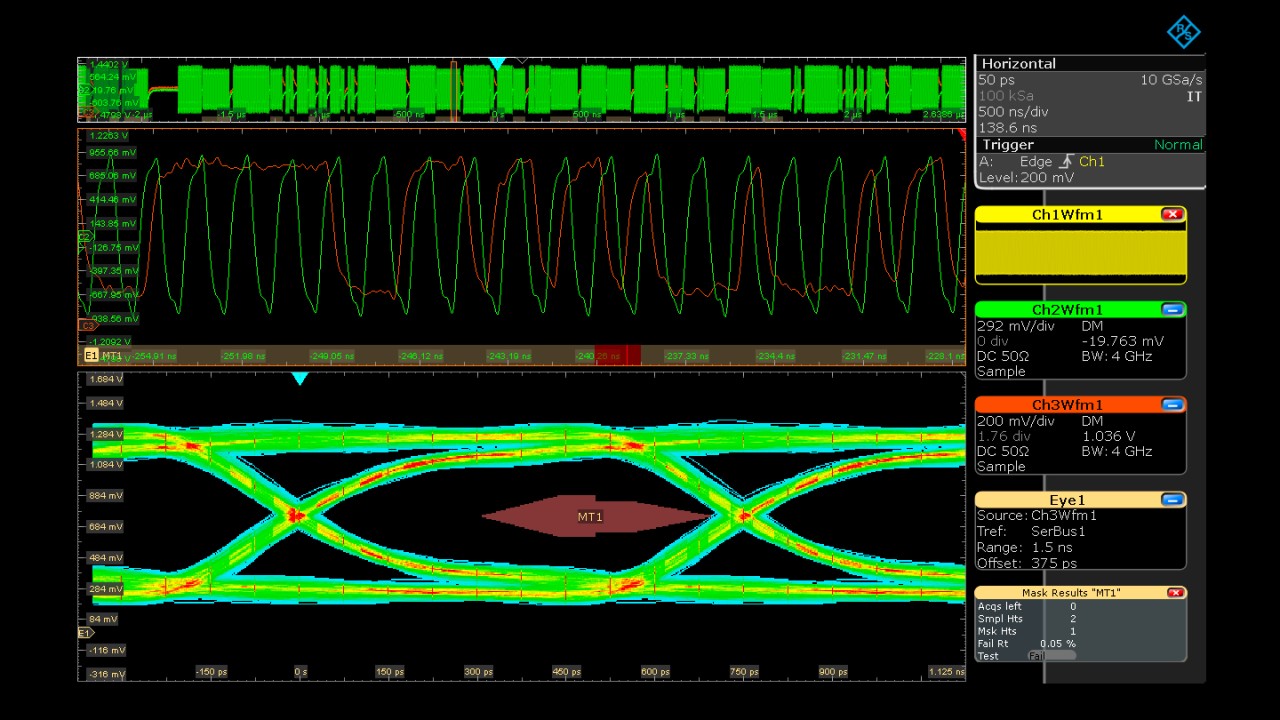

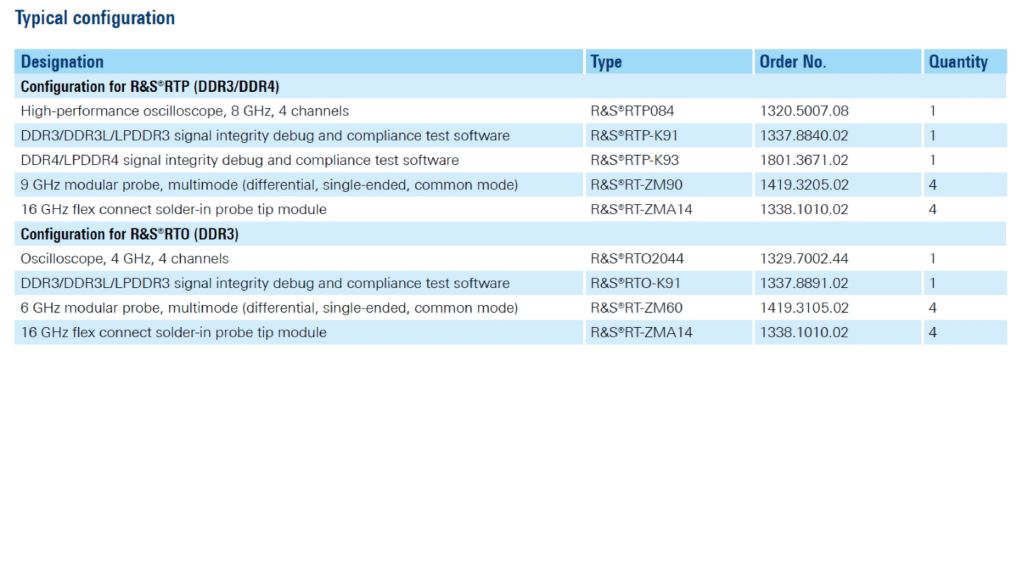

I test di conformità sono essenziali per assicurarsi che i segnali delle memorie dinamiche ad accesso casuale (DRAM) soddisfino le specifiche JEDEC relative a parametri quali la temporizzazione, la velocità di variazione dei segnali e i livelli di tensione. Per la verifica del sistema e il debugging, le misure con diagrammi a occhio sono gli strumenti più importanti per analizzare in modo efficiente l’integrità del segnale in qualsiasi progetto digitale. La particolare natura del bus DDR richiede una soluzione dedicata con una potente capacità di separazione tra i segnali di lettura/scrittura, per ottenere diagrammi a occhio significativi per il bus dati DDR.