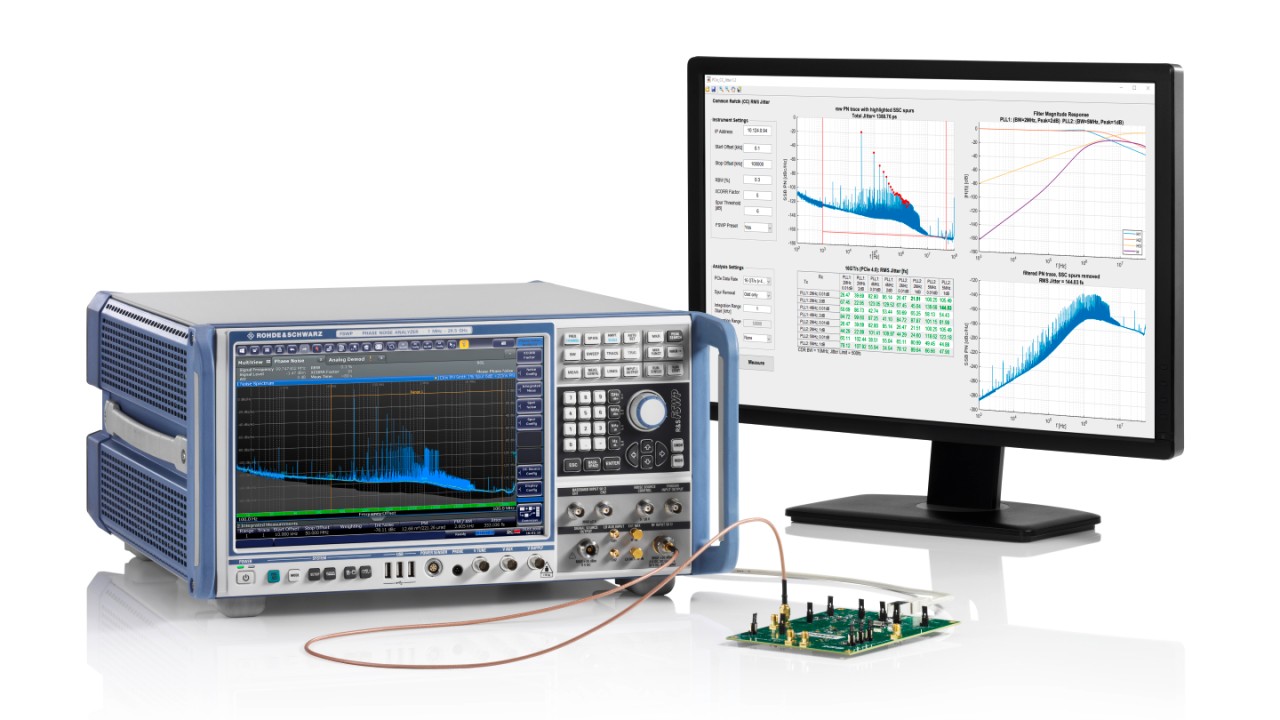

Soluzione Rohde & Schwarz

La misura del jitter del segnale di clock di solito comprende:

- Misura del rumore di fase

- Ponderazione del rumore di fase in base alla funzione di trasferimento del sistema corrispondente

- Integrazione del rumore di fase ponderato nella gamma di integrazione del jitter definito

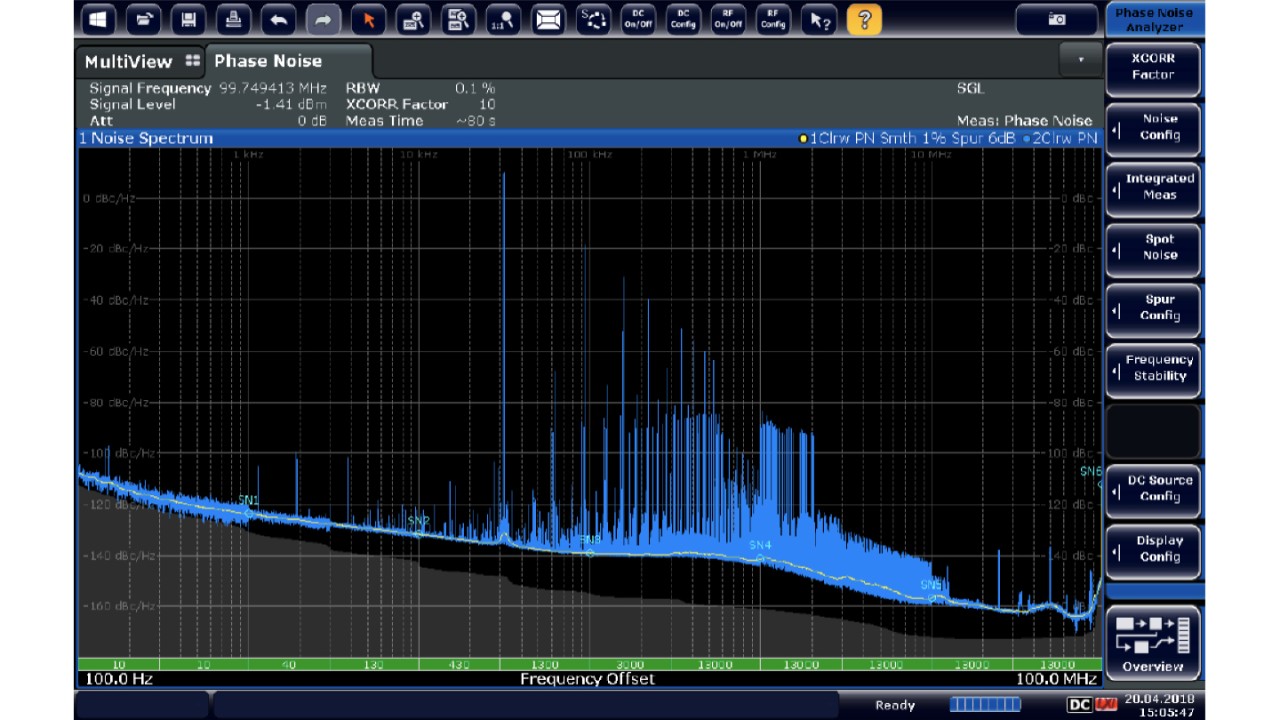

Misura del rumore di fase

Per un segnale di clock con un'elevata velocità di variazione dei fronti (slew rate), il jitter è determinato principalmente dal rumore di fase del segnale di clock. Poiché il rumore AM viene notevolmente soppresso dall'elevata velocità di variazione del segnale di clock, di solito non contribuisce al jitter di clock complessivo. Per effettuare misure accurate del jitter del segnale di clock, è importante un'elevata soppressione della modulazione d'ampiezza nella misura del rumore di fase.

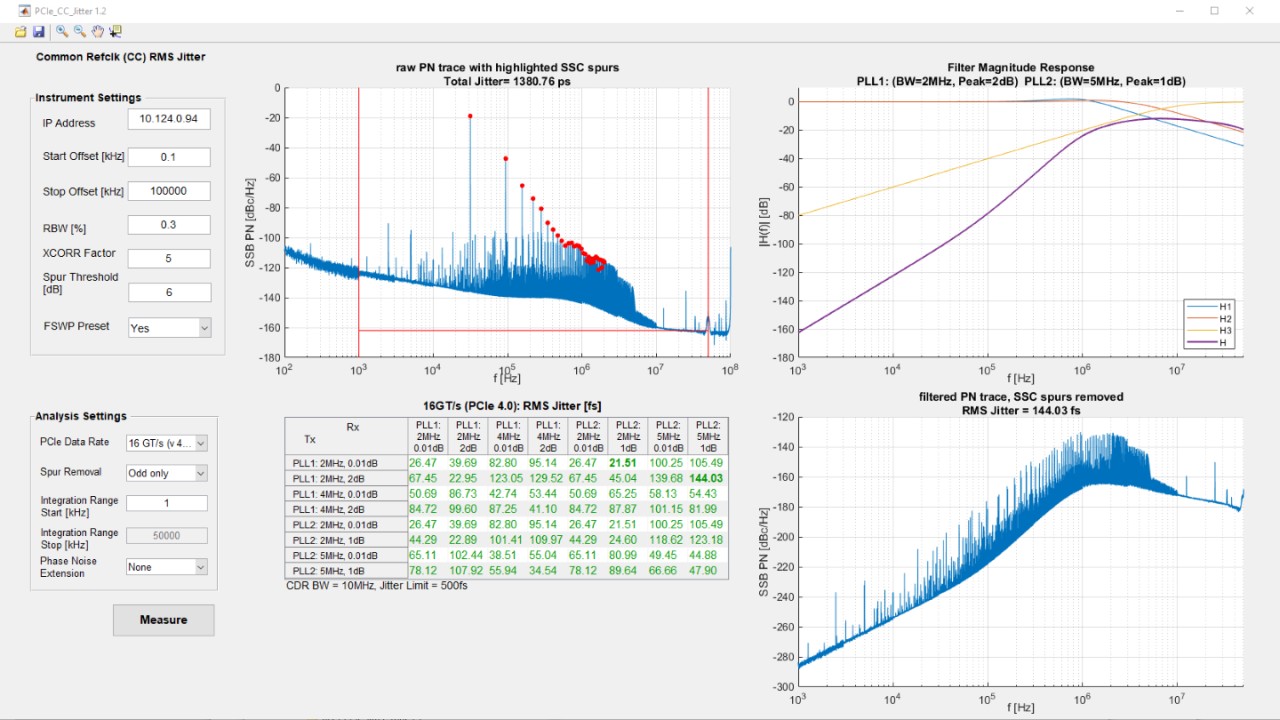

Ponderazione del rumore di fase

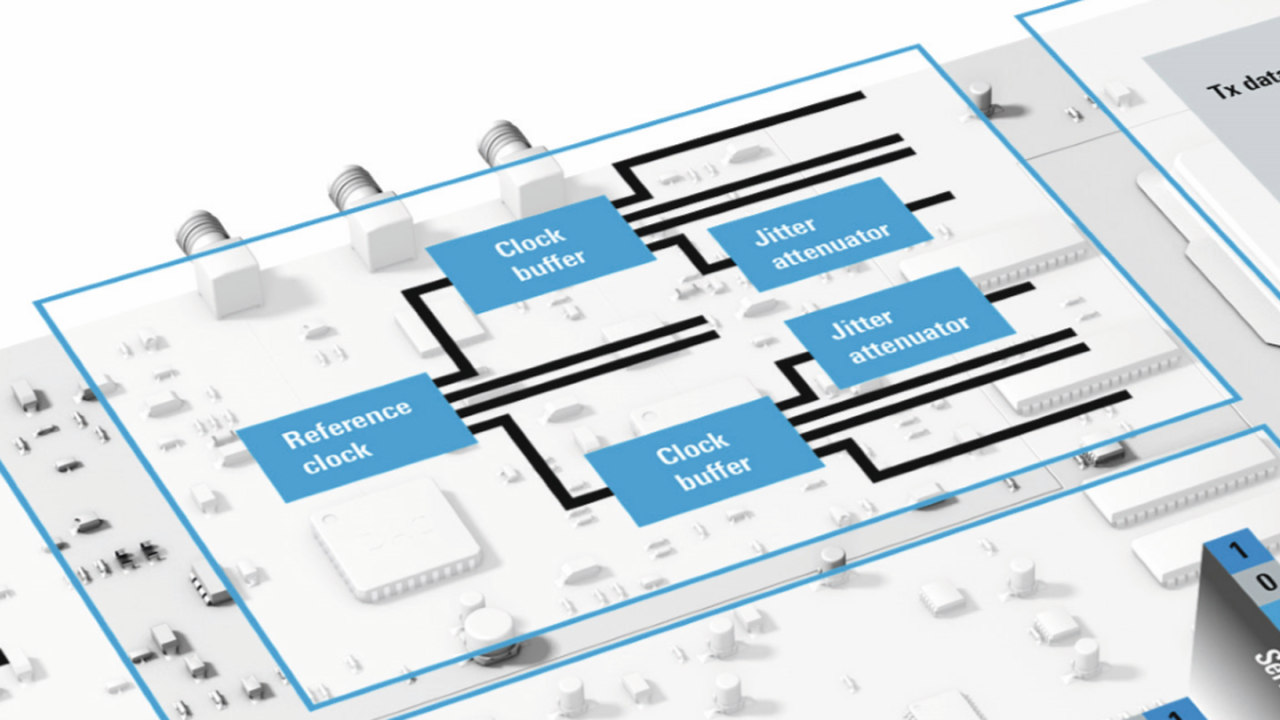

Le misure del jitter nei bus ad alta velocità, come PCIe, di solito devono includere gli effetti di sistema delle funzioni di trasferimento TX PLL, RX PLL e CDR. La funzione di trasferimento risultante complessiva è applicata alla traccia del rumore di fase misurato come filtro di ponderazione prima di integrare il jitter nella gamma definita di integrazione del jitter.

Integrazione del rumore di fase ponderato

Il rumore di fase ponderato è tipicamente integrato fino alla frequenza di Nyquist del segnale di clock (metà della velocità del clock), e in alcuni casi anche oltre. In tal caso, anche il rumore di fase deve essere misurato fino agli offset di frequenza più elevati.