Clock and LO components in 5G base stations (part 1/3)

R&S®SMW200A vector signal generator

Product information

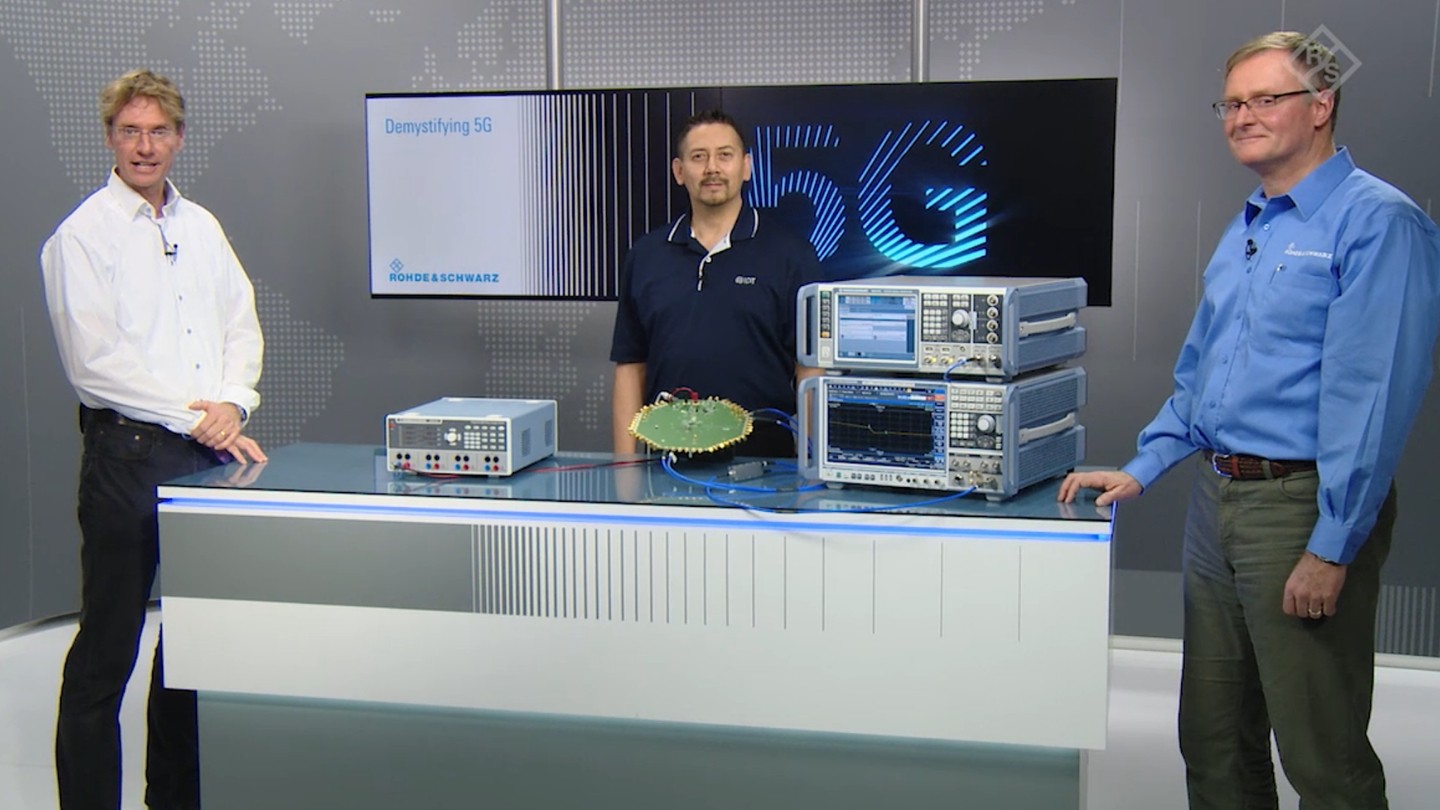

Monitoring and relocking clock inputs are critical for the performance and the timing of 5G base station transceivers. See how to measure the relocking period parameters of IDT’s RF sampling clock generator / jitter attenuator with vector signal generator R&S SMW200A incl. phase noise profile option and high-performance spectrum and phase noise analyzer R&S FSWP.