Rohde & Schwarz solution

The R&S®FSWP phase noise analyzer and VCO tester has an industry-leading phase noise sensitivity that can be further improved via the R&S®FSWP-B60 cross-correlation and R&S®FSWP-B61 cross-correlation (low phase noise) options.

With the R&S®FSWP-B64 residual phase noise measurements option, the instrument includes an ultra low phase noise signal source for easy additive phase noise measurements.

Alternatively, an external signal source like the R&S®SMA100B RF and microwave signal generator can be used to stimulate the tested PLL. The R&S®SMA100B provides best signal purity and phase noise performance and is scalable with different phase noise performance options.

For most SerDes PLLs and clock synthesizers, the phase noise of the R&S®FSWP-B64 and the R&S®SMA100B is negligible compared to the additive phase noise of the DUT. The phase noise measured by the R&S®FSWP mainly represents the additive phase noise of the DUT.

With the additive phase noise measurement method, included in the R&S®FSWP-B64, the phase noise influence of the stimulus signal can be suppressed even further 1). In contrast to other solutions, there is no need to manually achieve orthogonality with an external phase shifter. The R&S®FSWP automatically takes care of that, setting a new standard in user-friendly additive phase noise measurements.

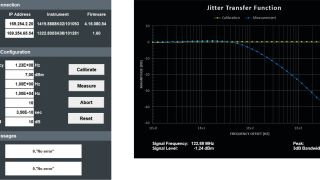

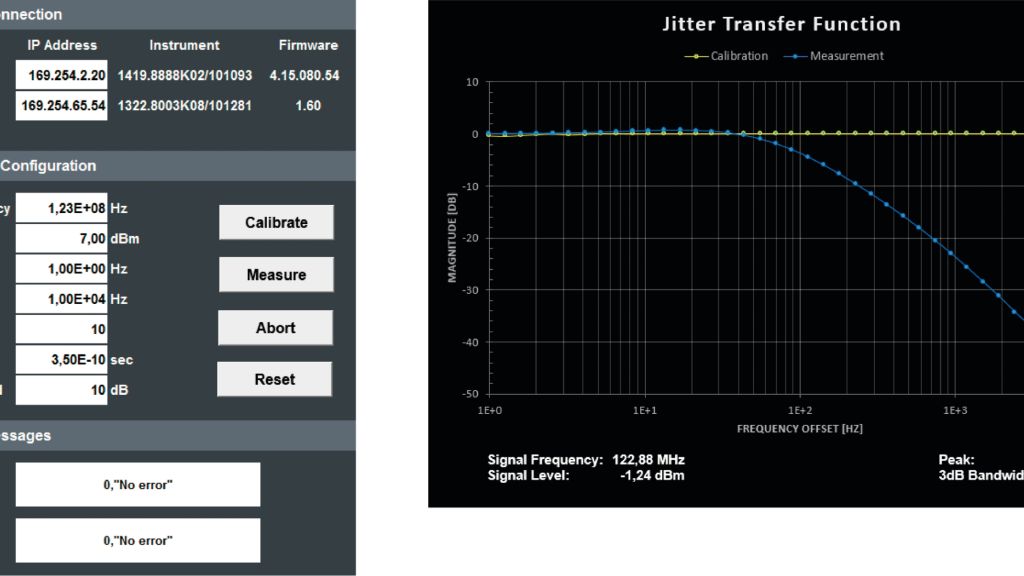

The R&S®SMA100B can also be used to measure the jitter transfer function of the PLL. Via PM modulation (R&S®SMAB-K720 option), artificial jitter is added to the signal source.

The R&S®FSWP measures the actual jitter at the DUT output and normalizes it to the jitter at the DUT input to determine the jitter attenuation. An external tool can be found in the download section of this application card. Besides R&S®SMA100B (R&S®SMAB-K720 option required), it supports the R&S®FSWP (requires R&S®FSWP-B60 or R&S®FSWP-B61 option) as well as the R&S®FSPN. The tool measures the jitter attenuation at various frequency offsets and provides the jitter transfer function of the DUT, including its peak and 3 dB bandwidth (see screenshots below).