PCIe – Successfully verify and optimize your system design

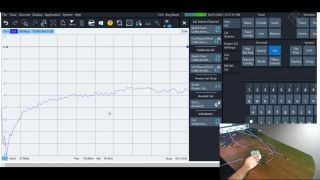

Design verification and debugging - Compliance testing

The PCIe architecture is the core of most computer designs and connects the processor and memory subsystems to the endpoint devices via the root complex. The growing demand for speed is driving standardization efforts in PCI-SIG and their adoption in data centers, PCs and embedded applications. Working closely with PCI-SIG, Rohde & Schwarz provides a wide range of solutions for PCIe compliance testing.

In addition to compliance testing, Rohde and Schwarz PCIe test solutions help you efficiently verify and debug your design at the board and system level, including in the presence of other interfaces and wireless signals.