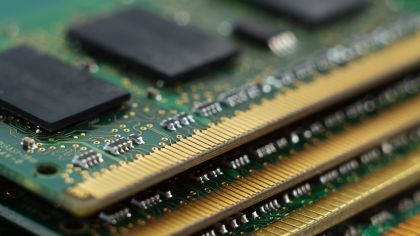

DDR memory testing

As is usually the case with a high-speed serial data bus, oscilloscopes can handle virtually all of the requirements for testing double data rate (DDR) data transfers and signal properties, both during development and for DDR compliance testing. At the physical layer, network analyzers can provide the highest level of accuracy for signal integrity testing. It is critical for manufacturers of computers and all types of electronic devices that use Random Access Memory (RAM) to run programs, as well as for memory chip suppliers throughout the industry to conduct a DDR memory test during design and later for functional DDR verification and production quality control.

DDR basics

DDR technology for transferring memory to and from a processor was introduced in 1998 and is now in its fifth generation. DDR stands for “double” data rate; because there are two memory transfers per clock cycle. Previously, there was only one, so DDR quickly replaced SDRAM, or Synchronous Dynamic Random Access Memory. DDR now dominates read/write memory access for all types of small processors and computers. With each generation of DDR, data transfer rates and clock frequency have increased, while operating voltages and power consumption have decreased. The huge increase in performance and the lack of backward compatibility between generations means that multiple generations of DDR are in common use – from DDR5, introduced in top-end PCs in 2021, back to DDR2, introduced in 2003. While DDR2 components are still sold in large quantities because there are many processors using the technology, new development is strictly limited.