Vérification du niveau système et débogage de conceptions mémoire DDR3/4

Cette note d’application propose une présentation de la technologie mémoire DDR et explique les défis classiques, relatifs à la nature spécifique des données DDR, aux bus de contrôle / adresse et contrôle, et décrit les mesures typiques pour vérifier et déboguer les conceptions système DDR.

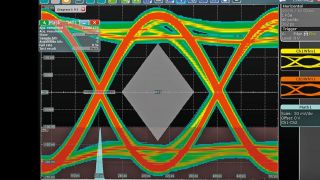

Le document explique les points de test recommandés et le branchement des sondes oscilloscopes, ainsi que la compensation des effets des inter-poseurs DDR via le de-embedding. Le document décrit la vérification efficace de l'intégrité du signal avec des mesures de diagramme de l’œil, des déclenchements avancés et des fonctionnalités TDR / TDT. Étant donné le nombre élevé de lignes de signaux et la terminaison du bus dynamique, le SSN (bruit de commutation simultanée) a un effet significatif sur les conceptions à mémoire DDR et sur l'intégrité du signal, ainsi que sur l'intégrité de puissance qui dépendent fortement de la configuration. Nous présentons des techniques permettant d'obtenir des taux d'acquisition élevés et qui permettent de détecter efficacement les pires scénarios, affectant la performance de la conception mémoire complète. Le document intègre également un aperçu sur l'intégrité de puissance.

En fournissant de bonnes pratiques au cours des processus de vérification de conceptions et de débogage, le document s'adresse à tous les concepteurs système et ingénieurs de test, travaillant sur des conceptions à mémoire DDR.