Rohde & Schwarz solution

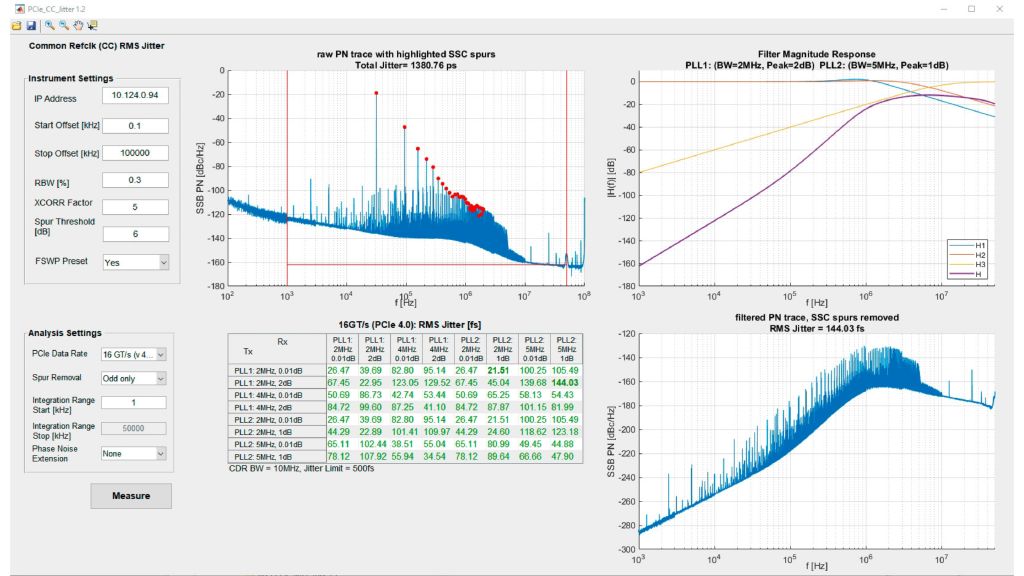

Measuring clock jitter typically consists of:

- Measuring the phase noise

- Weighting the phase noise based on the corresponding system transfer function

- Integrating the weighted phase noise in the defined jitter integration range

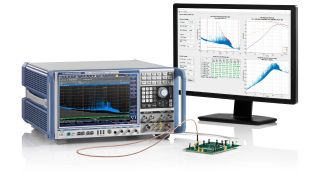

Measuring the phase noise

For clocks with a high slew rate, the clock jitter is mainly determined by the phase noise of the clock. Since AM noise is greatly suppressed by the high slew rate of the clock, it typically does not contribute to the overall clock jitter. For accurate clock jitter measurements, high AM suppression in the phase noise measurement is important.

Weighting the phase noise

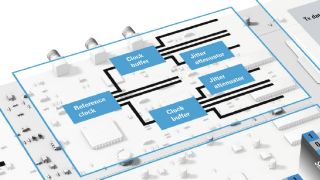

Jitter measurements in high-speed technologies like PCIe typically need to include the system effects of the TX PLL, RX PLL and CDR transfer functions. The resulting overall system transfer function is applied to the measured phase noise trace as a weighting filter before integrating the jitter in the defined jitter integration range.

Integrating the weighted phase noise

The weighted phase noise is typically integrated up to the Nyquist frequency of the clock (half of clock rate), and in some cases even above. In that case, the phase noise also needs to be measured up to higher frequency offsets.