Trigger no preâmbulo do DQS

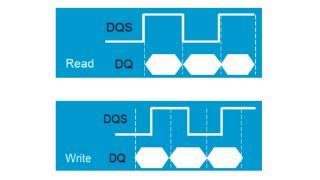

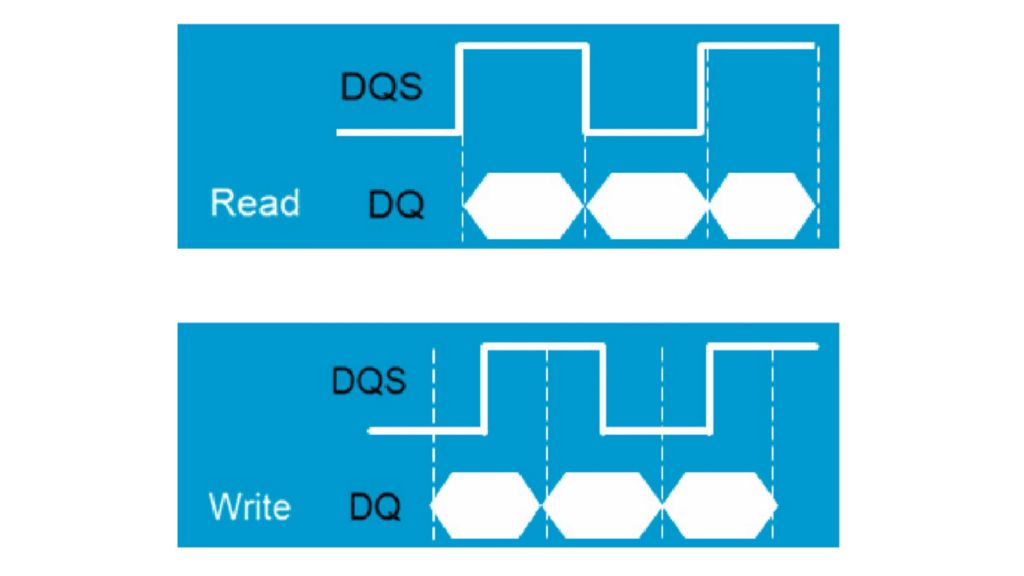

Para DDR3, o bit de preâmbulo DQS é positivo em ciclos de gravação e negativo em ciclos de leitura. Controladores DRAM geralmente têm uma largura de bit de preâmbulo ligeiramente diferente em comparação à largura do bit de dados. Isso pode ser usado como um diferenciador para triggering. Simplesmente defina o trigger de largura em pulsos mais longos que 1 UI ou use um intervalo de 1 UI a 1,5 UI. Uma vez que há diferentes implementações de preâmbulo, é recomendável primeiro observar a característica de tempo de preâmbulo do dispositivo.

Trigger da zona

O R&S®RTP oferece um trigger de zona opcional útil para qualificar ciclos de leitura e gravação válidos com base em forma de onda características. As zonas podem ser definidas livremente direto na tela para distinguir se os sinais devem ou não passar por elas. Isso é especialmente útil quando a característica da forma de onda fica fora da definição do trigger.

Para ciclos de gravação, DQS está fora de fase com DQ. É possível definir uma zona para garantir que o sinal DQ não viole a mesma borda que DQS.

Normalmente, a integridade de sinal da memória DDR é medida no lado da DRAM. Isso significa que o sinal de gravação tem uma amplitude de tensão menor que o sinal de leitura. Portanto, áreas da zona podem desqualificar ciclos de leitura com base na intensidade do sinal (nível de tensão).