Verificação de nível de sistema e depuração de designs de memória DDR3/4

Essa nota de aplicação oferece uma introdução à tecnologia de memória DDR e explica desafios comuns, relacionados à natureza específica de dados DDR, comando/endereço, barramentos de controle e descreve medições típicas para verificar e depurar designs de sistemas DDR.

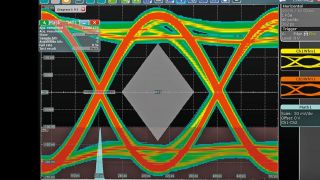

A publicação explica os pontos de teste recomendados e a conexão de pontas de prova de osciloscópios, bem como a compensação de efeitos de interpositores DDR. O documento descreve a verificação eficiente de integridade de sinal com medições de diagrama de olhos, triggering avançado e funcionalidade TDR/TDT. Dado o número de linhas de sinal e terminações de barramento, o ruído de comutação simultânea (SSN) tem efeito significativo nos designs de memória DDR; e a integridade de sinal, bem como a integridade de potência, são altamente dependentes de padrões. Apresentamos técnicas para alcançar altas velocidades de aquisição e ajudar a detectar com eficiência os casos mais difíceis que podem afetar o desempenho do design geral da memória. O documento também inclui um exame detalhado da integridade de potência.

Ao oferecer exemplos de boas práticas em verificações de design e processos de depuração, o documento é direcionado a todos os desenvolvedores e engenheiros de teste que trabalham com designs de memória DDR.