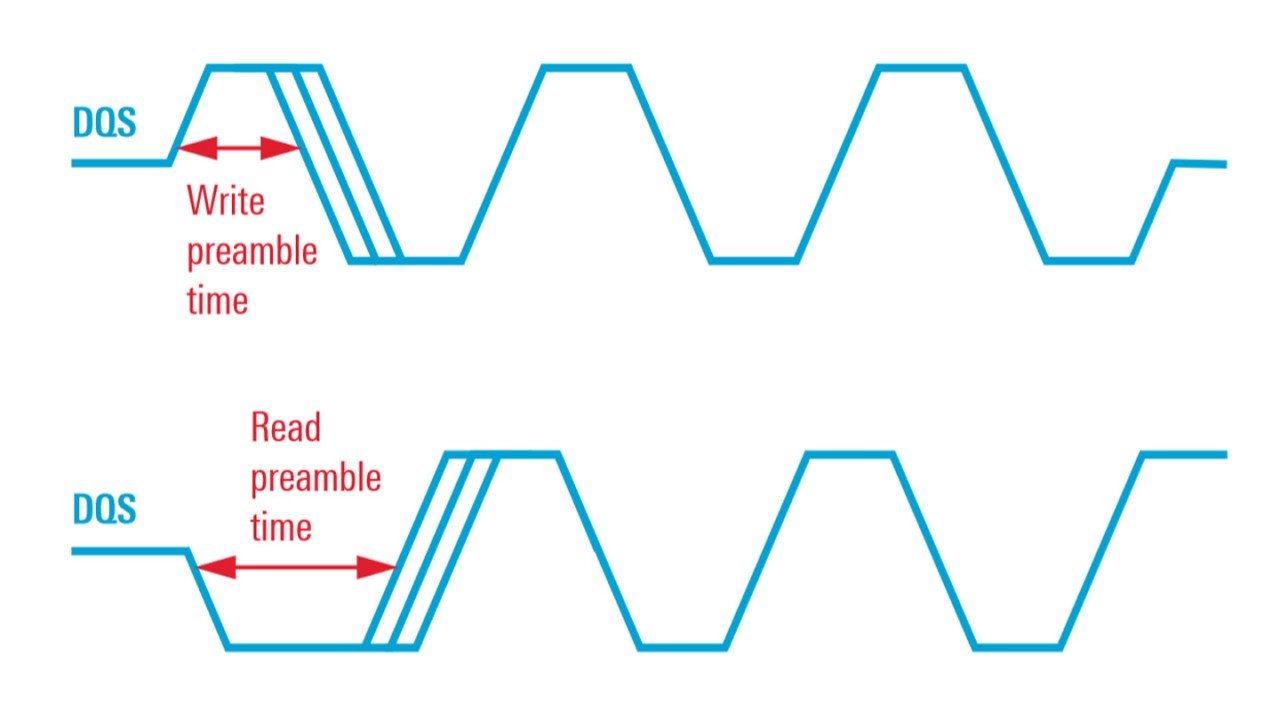

Triggern auf die DQS-Präambel

Im Fall von DDR3 ist das DQS-Präambel-Bit positiv in Schreibzyklen und negativ in Lesezyklen. DRAM-Controller haben in der Regel eine Präambel-Bitbreite, die etwas von der Datenbitbreite abweicht. Dies kann als Unterscheidungsmerkmal zum Triggern genutzt werden. Definieren Sie dazu einfach den Breitentrigger für Pulse, die länger als 1 UI sind, oder verwenden einen Bereich von 1 UI bis 1,5 UI. Da es unterschiedliche Präambel-Implementierungen gibt, empfiehlt es sich, zunächst die Präambelzeiten des Bauelements zu beobachten.

Zonentrigger

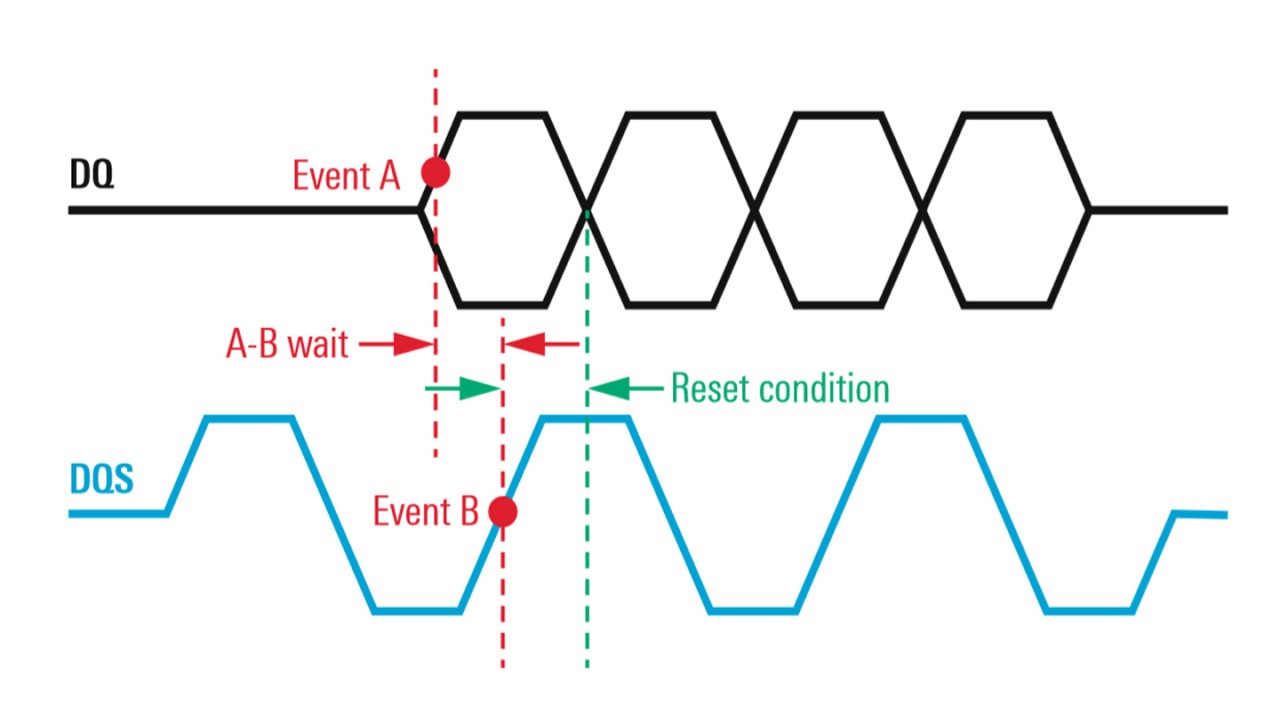

Für das R&S®RTP ist ein optionaler Zone Trigger verfügbar, der nützlich zur Beurteilung gültiger Lese- und Schreibzyklen auf Grundlage bestimmter Signalformen ist. Die Zonen können direkt auf dem Bildschirm frei definiert werden, um zu entscheiden, ob Signale durchgelassen werden sollen oder nicht. Dies ist insbesondere dann nützlich, wenn die Signalformeigenschaften nicht der Trigger-Definition entsprechen.

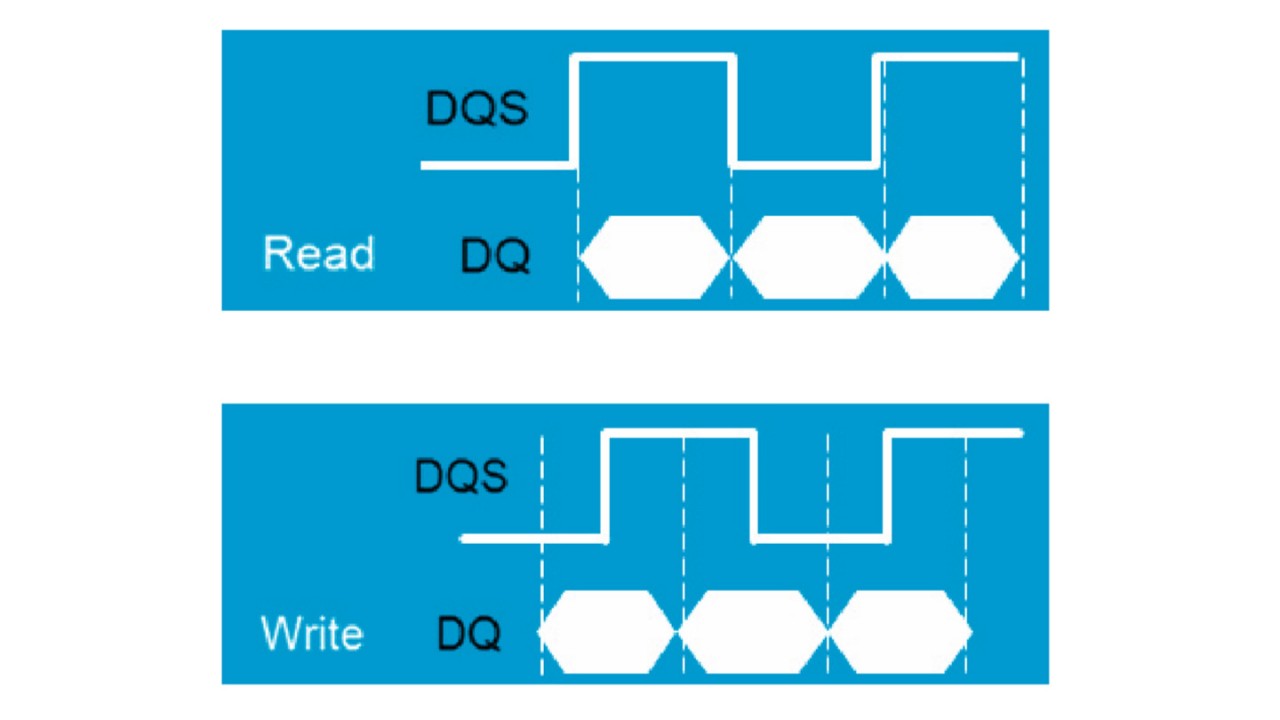

Bei Schreibzyklen ist DQS nicht mit DQ in Phase. Es kann eine Zone definiert werden, um sicherzustellen, dass das DQ-Signal nicht die Flanke des DQS-Signals verletzt.

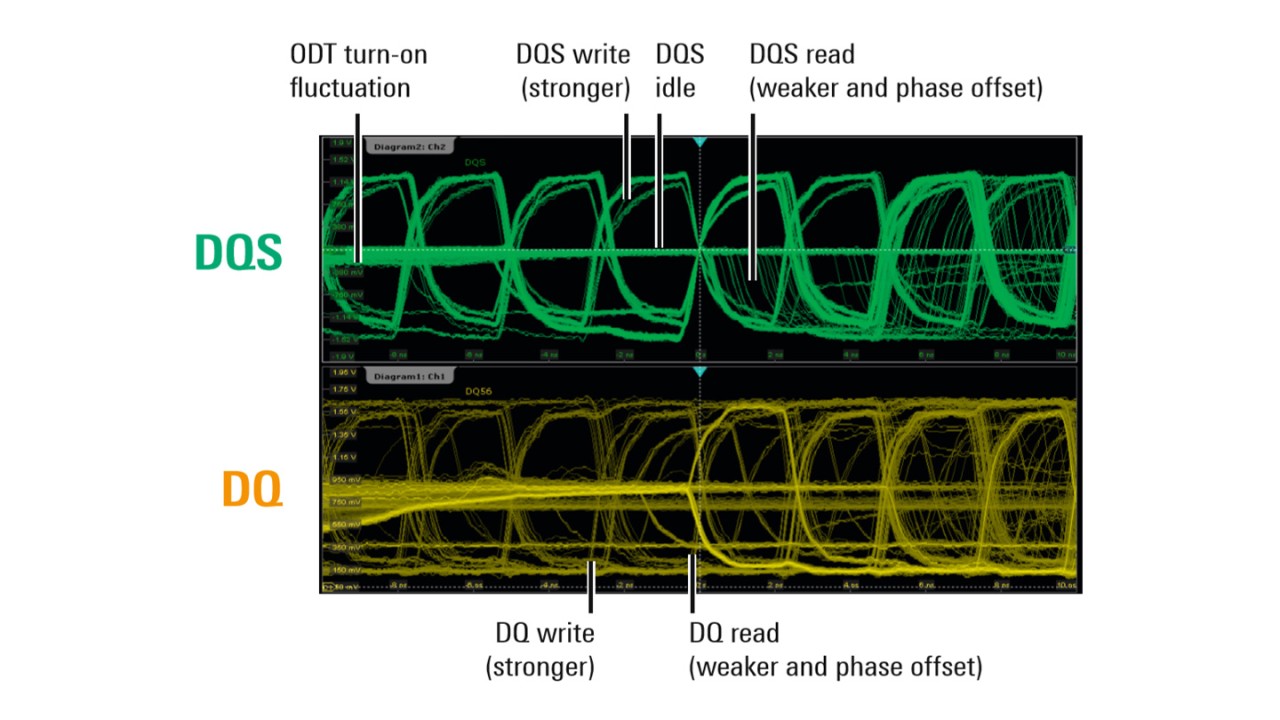

Normalerweise wird die Signalintegrität des DDR-Speichers auf der DRAM-Seite gemessen. Das bedeutet, dass das Schreibsignal eine niedrigere Spannungsamplitude hat als das Lesesignal. Deswegen können die Lesezyklen mit Hilfe von Zonenbereichen anhand der Signalstärke (Spannungspegel) aussortiert werden.