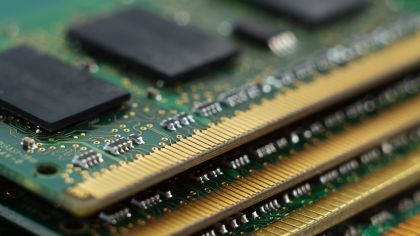

DDR 메모리 테스트

고속 시리얼 데이터 버스의 경우와 같이, 오실로스코프는 개발 및 DDR 컴플라이언스 테스트단계에서 DDR(Double Data Rate)데이터 전송 및 신호 특성 테스트에 대한 요구사항을 거의 모두 처리할 수 있습니다. 물리적 계층에서 네트워크 분석기는 신호 무결성 테스트에 대해 가장 높은 수준의 정확도를 제공할 수 있습니다. 컴퓨터와 RAM(Radom Access Memory)을 탑재한 일체의 전자기기를 제조하는 업체는 프로그램을 실행하는 것이 중요하며 산업 전반의 메모리 칩 공급업체는 설계 단계와 이후 단계에서 기능적 DDR 검증및 생산 품질 관리를 위해 반드시 DDR 메모리 테스트를 수행해야 합니다.

DDR 기초 정보

DDR기술은 프로세서 사이에서 메모리를 전송하기 위한 목적으로 1998년 소개되었으며 최신 버전은 5세대입니다. DDR은 “Double” Data Rate의 약자로, 클록 사이클 당 두 번의 메모리 전송이 이루어진다는 의미입니다. 이전에는 한 번의 메모리 전송만 지원되었기 때문에 DDR은 SDRAM(Synchronous Dynamic Random Access Memory)을 빠르게 대체하였습니다. 이제 모든 종류의 소형 프로세서 및 컴퓨터에서 읽기/쓰기 메모리 액세스에 DDR이 사용되고 있습니다. 새로운 DDR 세대가 개발될 때마다 데이터 전송 레이트와 클록 주파수가 증가되었고 작동 전압 및 전력 소비는 감소하였습니다. 대폭적인 성능 향상이 이루어지고 세대 간 역호환성이 지원되지 않음에 따라 2021년 최상급 PC에 적용된 DDR5부터 2003년 출시된 DDR2까지 여러 세대의 DDR이 함께 사용되고 있습니다. DDR2 기술을 사용하는 프로세스가 많으므로 여전히 대량의 DDR2 구성요소가 판매되고 있지만 새로운 개발은 매우 제한적입니다.