Trigger on DQS preamble

For DDR3, the DQS preamble bit is positive on write cycles and negative on read cycles. DRAM controllers typically have a slightly different preamble bit width compared to the data bit width. This can be used as a differentiator for triggering. Simply define the width trigger on pulses longer than 1 UI or use a range from 1 UI to 1.5 UI. Since there are different preamble implementations, it is recommended to first observe the preamble timing characteristic of the device.

Zone trigger

The R&S®RTP offers an optional zone trigger, which is useful for qualifying valid read and write cycles based on distinctive waveform shapes. Zones can be freely defined directly on the screen to distinguish if signals should or should not pass through them. This is especially useful when the waveform characteristic falls out of the trigger definition.

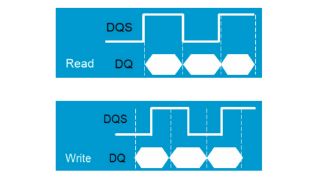

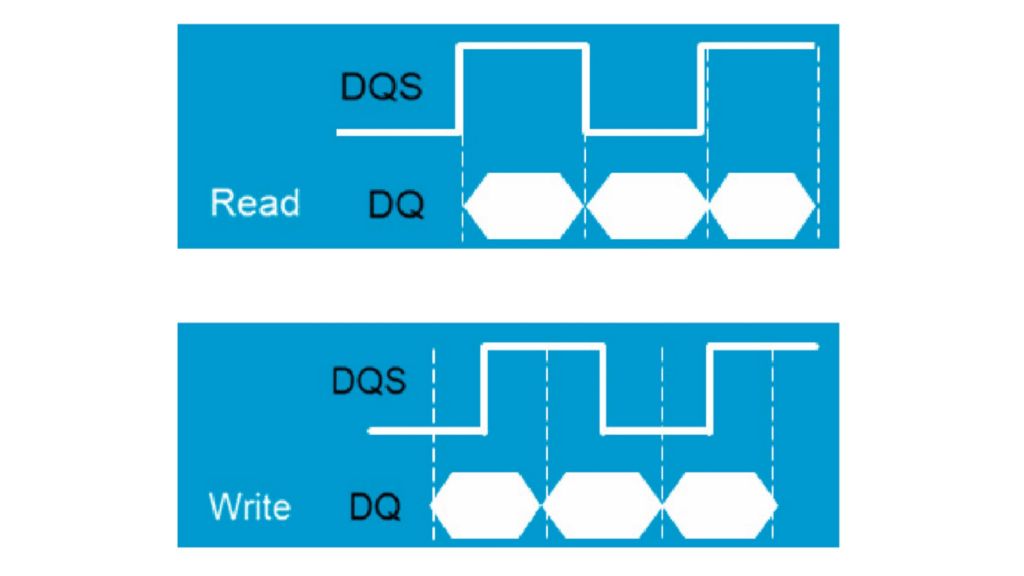

For write cycles, DQS is out of phase with DQ. A zone can be defined to ensure that the DQ signal does not violate the same edge as DQS.

Normally, the signal integrity of the DDR memory is measured on the DRAM side. This means that the write signal has a lower voltage amplitude than the read signal. Therefore, zone areas can disqualify read cycles based on signal strength (voltage level).