DDR3メモリのリードサイクルおよびライトサイクルのトリガ

DDRインタフェースのシグナルインテグリティー性能を解析する際には、リードサイクルとライトサイクルを分離することが困難な課題になっていました。特にリアルタイムでアイダイアグラムを再現しようとする場合には、さまざまなトリガ機能が必要になります。

DDRインタフェースのシグナルインテグリティー性能を解析する際には、リードサイクルとライトサイクルを分離することが困難な課題になっていました。特にリアルタイムでアイダイアグラムを再現しようとする場合には、さまざまなトリガ機能が必要になります。

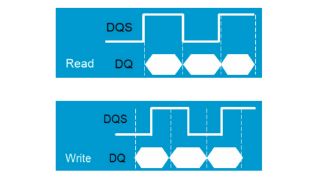

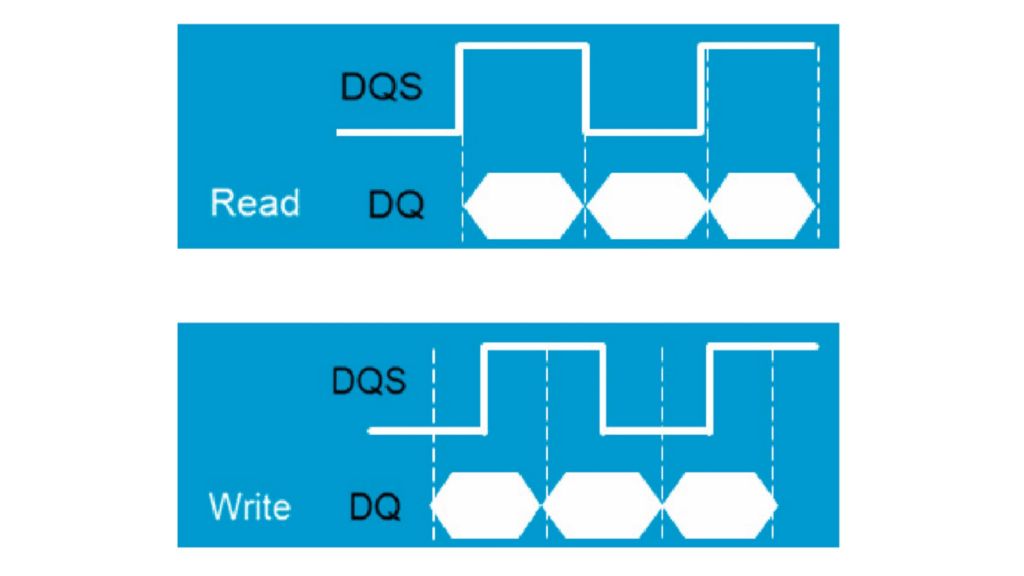

DDRインタフェースの信号品質は、信頼性の高いメモリシステム動作を実現する上で非常に重要です。データアイ解析は、シグナルインテグリティーを評価する際に一般的に用いられる方法です。DDRアーキテクチャーでは半二重動作を使用します。この場合、リードサイクルとライトサイクルが同じ信号トレース上で異なるタイムインターバルで実行されます。アイ解析でリードサイクルとライトサイクルを区別するため、エンジニアはデータ信号(DQ)とストローブ信号(DQS)の位相調整を確認します。専用のトリガ機能を使用してリードサイクルとライトサイクルを分離するのは困難ですが、リアルタイムで長時間にわたるデータアイの評価を行うことは可能です。

リードサイクルとライトサイクル

R&S®RTP 高性能オシロスコープは、高度なトリガ機能を備えています。独自のデジタル・トリガ・システムのA-Bシーケンスにより、高精度な時間遅延と1 psまでの分解能に対応した2つの連続するトリガ条件をセットアップすることができます。トリガ条件には、他のチャネルのロジッククオリファイアを組み合わせることができます。さらに、R&S®RTP-K19 ゾーン・トリガ・オプションを使用すると、トリガ条件を視覚的に特定するゾーンを定義できるため、セットアップを簡素化することができます。

リードサイクルとライトサイクル

DDRメモリインタフェースのリードサイクルとライトサイクルは、位相調整されていません。このアーキテクチャーでは、ハイまたはローで安定しているときにデータ(DQ)をラッチするように、メモリコントローラーで差動ストローブ信号(DQS)を提供する必要があります。リードサイクルではDRAMからメモリコントローラーにDQSとDQが同じ位相で送信されますが、ライトサイクルの場合は0.5ユニットインターバル(UI)のオフセットが存在します。

遅延のあるA-Bトリガのセットアップ

ライトサイクルでの位相関係を利用して、AトリガイベントをDQ信号上のエッジトリガとして定義することができます。次に、遅延およびリセットメカニズムで、DQS信号上のイベントBのエッジトリガを確認するように制限します。イベントBを確認するための遅延は、½ UI未満である必要があります。

また、イベントAでは、トライステートシーケンスから復帰した後の最初のDQビットを検知するウィンドウトリガを使用する方法もあります(ウィンドウ幅 > 1 UI)。

DQSプリアンブルでのトリガ

DDR3の場合、DQSプリアンブルビットは、ライトサイクルでは正で、リードサイクルでは負になります。DRAMコントローラーは通常、プリアンブルビット幅とデータビット幅がわずかに異なっています。これは、トリガ用の差動要因として使用することができます。パルスで1 UIよりも長い幅トリガを定義するか、1 UI~1.5 UIの範囲を使用します。プリアンブルにはさまざまな実装が存在するため、最初にデバイスのプリアンブルタイミング特性をよく観察することをお勧めします。

DQSプリアンブルでのトリガ

DDR3の場合、DQSプリアンブルビットは、ライトサイクルでは正で、リードサイクルでは負になります。DRAMコントローラーは通常、プリアンブルビット幅とデータビット幅がわずかに異なっています。これは、トリガ用の差動要因として使用することができます。パルスで1 UIよりも長い幅トリガを定義するか、1 UI~1.5 UIの範囲を使用します。プリアンブルにはさまざまな実装が存在するため、最初にデバイスのプリアンブルタイミング特性をよく観察することをお勧めします。

ゾーントリガ

R&S®RTPでは、オプションでゾーントリガを利用できます。ゾーントリガは、明確な特徴を持つ波形形状に基づいて有効なリードサイクルとライトサイクルを特定するのに役立ちます。ゾーンは、画面上で直接自由に定義することができます。ゾーンを定義することで、信号がゾーンを通過するかどうかを見分けることができます。これは、波形の特性がトリガ定義から外れる場合に特に便利です。

ライトサイクルの場合、DQSとDQは位相がずれています。ゾーンを定義することで、DQ信号がDQSのエッジを侵害していないことを確認することができます。

通常、DDRメモリのシグナルインテグリティーは、DRAM側で測定します。これは、ライト信号の方がリード信号よりも電圧振幅が低いことを意味します。このため、ゾーン領域で、信号強度(電圧レベル)に基づいてリードサイクルを対象外にすることができます。

DDRメモリインタフェースのシグナルインテグリティーを評価する際には、リードサイクルとライトサイクルを確実に分離することが重要です。R&S®RTP 高性能オシロスコープのデジタルトリガを使用すると、高精度なシーケンシャルトリガのメカニズムを実現できます。これにゾーントリガを組み合わせることで、DDRメモリインタフェースの測定において汎用性に優れ柔軟性の高いトリガ機能を利用することが可能になります。