Disparo en preámbulo DQS

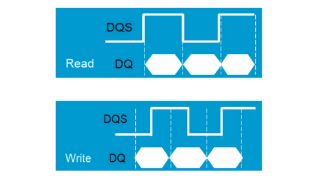

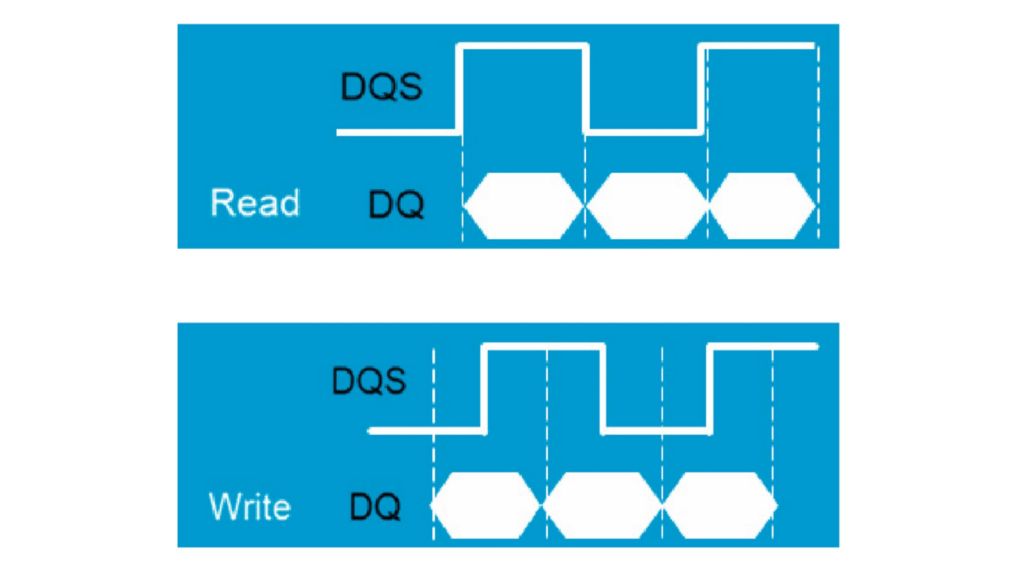

Para DDR3, el fragmento de preámbulo DQS es positivo en los ciclos de escritura y negativo en los ciclos de lectura. Los controladores DRAM suelen tener un ancho de bit de preámbulo ligeramente distinto si se compara con el ancho de bit de datos. Este dato puede utilizarse como diferenciador para el disparo. Solo debe definir el disparo de ancho en impulsos con duración superior a 1 UI o utilizar un rango de entre 1 y 1,5 UI. Dado que existen distintas aplicaciones del preámbulo, se recomienda observar primero las características de temporización de preámbulo del dispositivo.

Disparador de zona

El R&S®RTP ofrece un disparo de zona opcional, que resulta útil para evaluar los ciclos de lectura y escritura válidos en función de formas de onda diferenciadas. Las zonas pueden definirse con libertad directamente en la pantalla para distinguir si las señales deberían pasar o no a través de estas. Esto resulta especialmente útil cuando la característica de la forma de onda queda fuera de la definición de disparo.

Para los ciclos de escritura, la DQS está desfasada con la DQ. Es posible definir una zona para garantizar que la señal DQ no infrinja el mismo flanco que la DQS.

Normalmente, la integridad de señal de la memoria DDR se mide en el lado de la DRAM. Esto significa que la señal de escritura tiene una amplitud de tensión menor que la señal de lectura. Por ello, los distintos espacios de una zona pueden inhabilitar los ciclos de lectura en función de la intensidad de la señal (nivel de tensión).