Проверка и отладка памяти DDR3/4 на системном уровне

В этом руководстве по применению содержится обзор технологии работы памяти DDR, приведены часто встречающиеся проблемы, относящиеся к данным DDR, командам/адресам и шинам управления, и приводятся типичные измерения для проверки и отладки систем DDR.

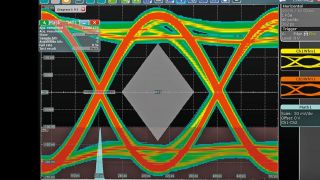

В документе описываются рекомендуемые контрольные точки и подключение осциллографических пробников, а также компенсация влияния интерпозеров для DDR с помощью исключения. Документ содержит описание эффективной проверки целостности сигнала с использованием измерений с помощью глазковой диаграммы, расширенных функций запуска и функциональных возможностей TDR/TDT. Из-за большого количества сигнальных линий и динамической оконечной нагрузки шин одновременные коммутационные помехи (SSN) оказывают существенное влияние на память DDR, а целостность сигнала и питания сильно зависят от шаблона. Мы расскажем о методах поддержки высокой скорости сбора данных и эффективного обнаружения наихудших сценариев, которые влияют на производительность всей памяти. Документ также содержит подробное описание целостности питания.

В документе приведены наилучшие примеры из практики проверки и отладки устройств; он будет полезен всем разработчикам систем и инженерам-испытателям, работающим с памятью DDR.