Запуск по преамбуле DQS

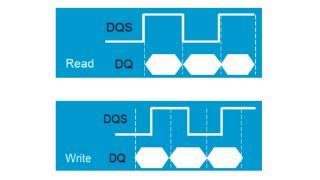

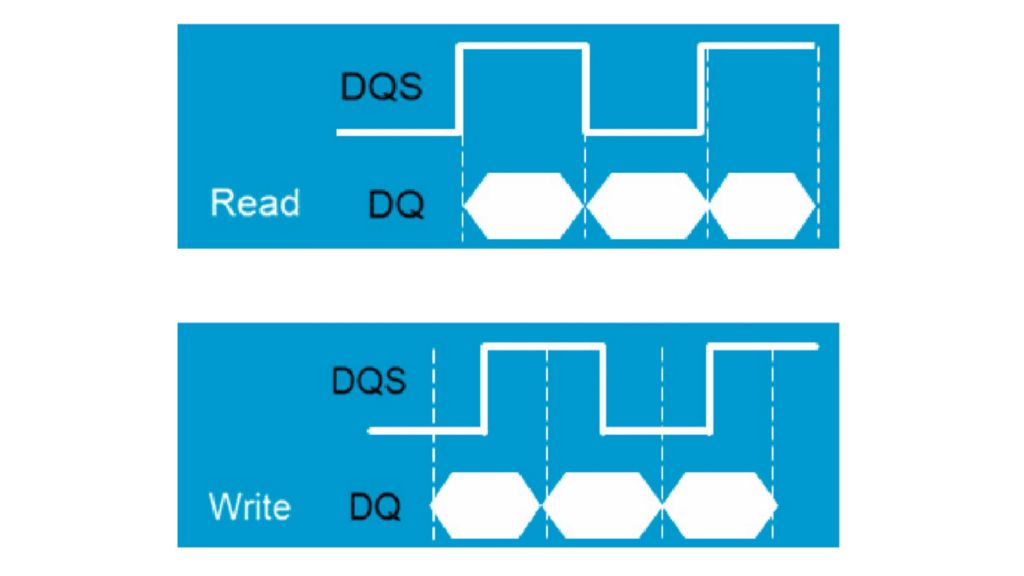

Для DDR3 бит преамбулы DQS положителен для циклов записи и отрицателен для циклов чтения. Обычно контроллеры DRAM имеют немного другую битовую ширину преамбулы по сравнению с битовой шириной данных. Это свойство можно использовать в качестве ключевого факта для запуска. Просто задайте ширину окна запуска по импульсам больше 1 UI или используйте диапазон от 1 UI до 1,5 UI. В связи с наличием различных реализаций преамбулы рекомендуется вначале оценить временную характеристику преамбулы устройства.

Зональный запуск

R&S®RTP предлагает дополнительный зональный запуск, который полезен для определения приемлемых циклов чтения и запуска на базе характерных форм сигнала. Зоны могут быть заданы прямо на экране для определения того, должны или не должны проходить через них сигналы. Это особенно полезно, когда характеристика сигнала выходит из области определения запуска.

Для циклов записи сигнал DQS по фазе не совпадает с DQ. Чтобы сигнал DQ не выходил за границу сигнала DQS, можно задать определенную зону.

Обычно целостность сигнала памяти DDR измеряется на стороне DRAM. Это означает, что сигнал записи имеет меньшую амплитуду по напряжению по сравнению с сигналом чтения. В связи с этим зональные области могут негативно характеризовать циклы чтения на базе интенсивности сигнала (уровня напряжения).