Trigger sul preambolo DQS

Per le memorie DDR3, il bit di preambolo DQS è positivo nei cicli di scrittura e negativo in quelli di lettura. Di norma i controller DRAM hanno un’ampiezza del bit di preambolo leggermente diversa rispetto a quella del bit di dati. Questo elemento può fungere da differenziatore per il triggering. basta definire il trigger basato sulla larghezza impostandolo su impulsi di durata superiore a 1 UI o usare un intervallo compreso tra 1 UI e 1,5 UI. Poiché le implementazioni dei preamboli variano, si raccomanda di osservare innanzitutto la temporizzazione del preambolo tipica del dispositivo in esame.

Trigger a zona

L’oscilloscopio R&S®RTP offre una modalità opzionale di trigger a zona, utile per l’identificazione di cicli di lettura e scrittura validi sulla base di caratteristiche distintive delle forme d’onda. Le zone possono essere definite liberamente, direttamente sullo schermo, per indicare se i segnali devono o non devono attraversarle. Ciò risulta particolarmente utile quando la caratteristica della forma d’onda non ricade nella definizione del trigger.

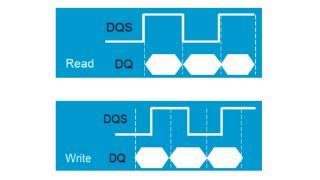

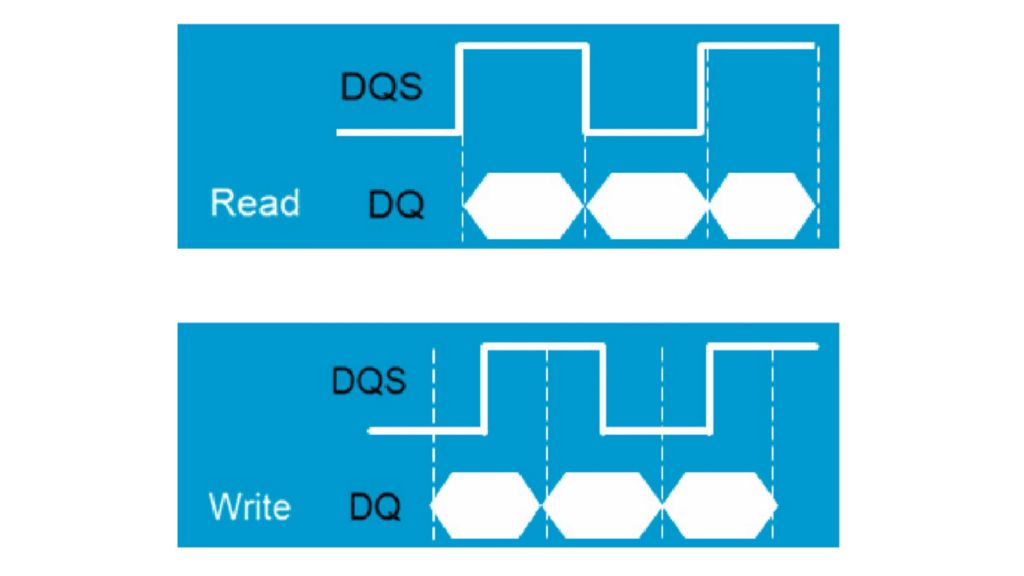

Nei i cicli di scrittura, i segnali DQS e DQ non sono allineati in fase. Può essere definita una zona per assicurare che il segnale DQ non violi lo stesso fronte del segnale DQS.

Di norma l’integrità del segnale delle memorie DDR si misura dal lato della DRAM. Ciò significa che il livello della tensione del segnale di scrittura è inferiore rispetto a quello del segnale di lettura. I cicli di lettura possono essere pertanto esclusi dalle zone in base all’intensità del segnale (livello di tensione).