デジタルデザインテスト

デザインを検証/デバッグするためのデジタルデザインテストソリューション

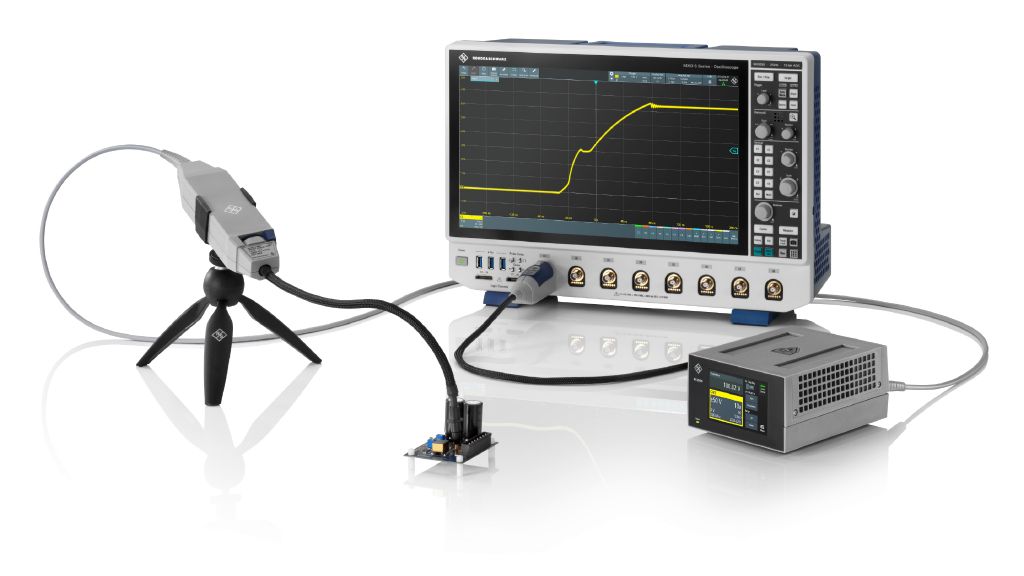

テクノロジーが急速に進化し続けるのに伴い、高速デジタル規格は、常に動向を見据え先手を打ちながらパワフルであり続けるために、市場ニーズに対応していく必要があります。電子技術者は、このような厳しい要件を満たす集積回路基板アーキテクチャーの設計および開発に直面しています。電子機器は世代ごとに、デジタルデザインの性能に対して新たな課題ももたらします。デジタルデザインシステムが、ますます増大する規格や課題に対応することを確実にする必要があるならば、デザインから完全なコンプライアンスまで製品開発サイクルのあらゆる段階でそれをテストする必要があります。デジタルデザインテストソリューションは、インターコネクト製品などのさまざまなデザインバリエーションに対応し、ジッタテストのような膨大な測定に対応するためのテストツールを提供する必要があります。

シグナルインテグリティーやパワーインテグリティーが、デジタルデザインに不可欠です。データレートの上昇、電源電圧の低下、集積密度の向上により、信号やクロックに課せられるジッタ/ノイズ制限を引き下げることが求められます。また、周波数依存損失、反射、クロストークなどの伝送チャネルの障害も激しくなり、電圧低下(サグ)やグラウンドバウンスがパワーレールに与える影響が増大します。さらに、電源電圧の低下により、パワーレール妨害波の許容値が小さくなり続け、信号やクロックにジッタが生じ、振幅雑音が付加されます。