Déclenchement sur préambule DQS

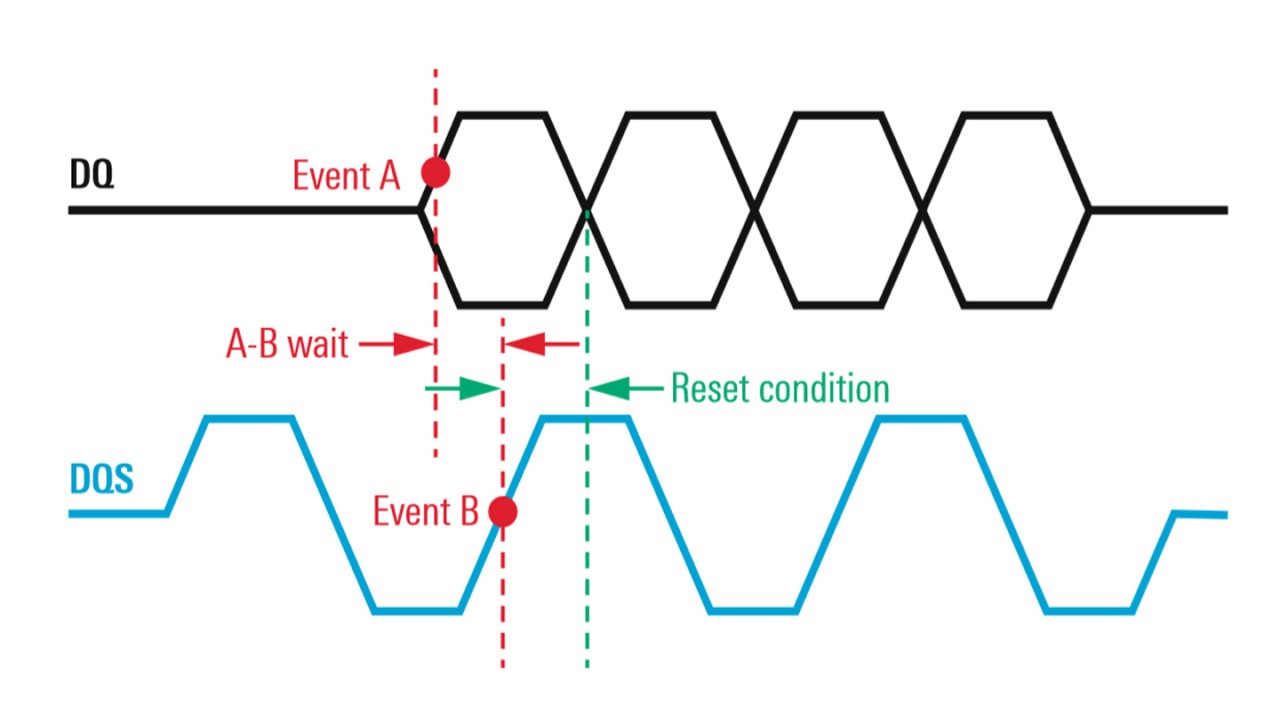

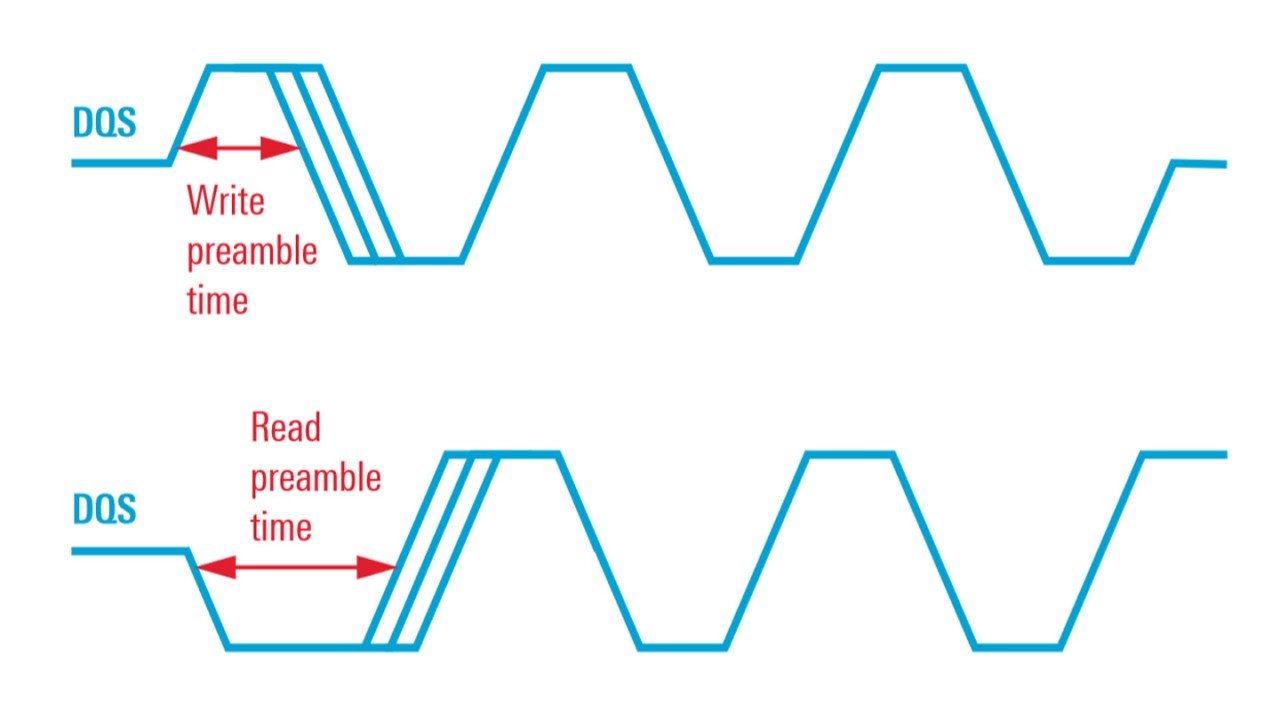

Pour DDR3, le bit de préambule DQS est positif dans les cycles d'écriture, négatif dans les cycles de lecture. Généralement les contrôleurs DRAM ont une largeur de bit de préambule légèrement différente de la largeur de bit de données. Cela peut servir de facteur de différenciation du déclenchement. Il suffit de définir le déclencheur de largeur sur les impulsions de longueur supérieure à 1 UI ou d'utiliser une plage comprise entre 1 UI et 1,5 UI. En raison de la mise en œuvre de différents préambules, il est recommandé d'observer en premier lieu les caractéristiques de synchronisation du préambule de l'appareil.

Déclenchement par zone

L'oscilloscope R&S®RTP propose un déclencheur par zone en option, utile pour la qualification des cycles de lecture et d'écriture valides, sur la base de formes d'ondes distinctives. Les zones peuvent être librement définies directement à l'écran, pour distinguer si les signaux doivent ou ne doivent pas les traverser. Ceci est particulièrement utile lorsque les caractéristiques de forme d'onde n'entrent pas dans la définition de déclenchement.

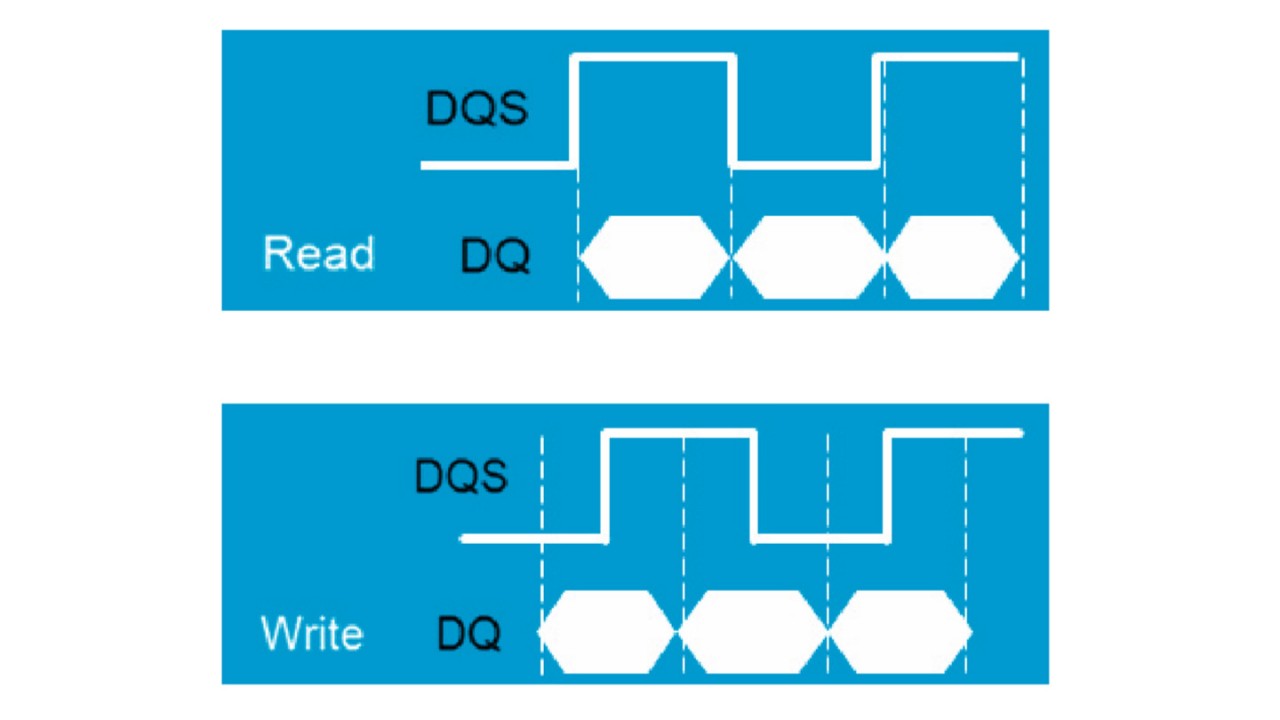

Pour les cycles d'écriture, le DQS n'est pas en phase avec le DQ. Une zone peut être définie pour s'assurer que le signal DQ ne viole pas le même bord que le DQS.

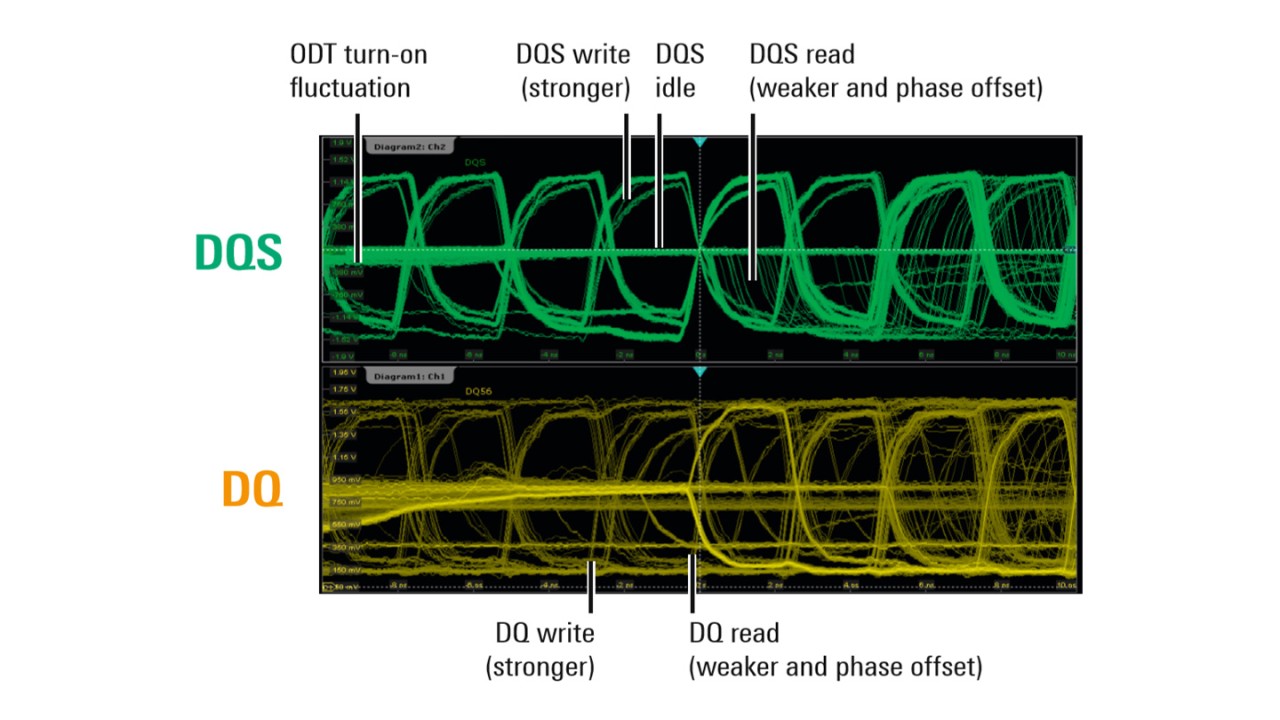

Généralement, l'intégrité du signal de la mémoire DDR est mesurée du côté DRAM. Cela signifie que l'amplitude de tension du signal d'écriture est inférieure à celle du signal de lecture. C'est pourquoi des régions de zone peuvent disqualifier des cycles de lecture en fonction de l'intensité du signal (niveau de tension).