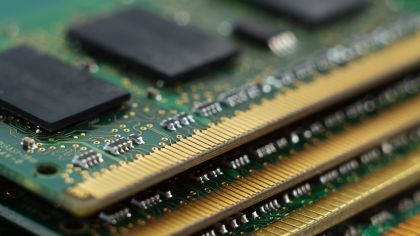

DDRメモリテスト

高速シリアルデータバスを扱う通常の場合と同様に、オシロスコープは、ほぼすべてのダブルデータレート(DDR)のテストに対応することができ、データ転送や信号特性を検証可能です。これは、開発時に限らず、DDRコンプライアンステストにも当てはまります。物理層では、ネットワーク・アナライザを使用して、最高レベルの確度でシグナルインテグリティーテストを実行できます。プログラムを実行するためのランダムアクセスメモリ(RAM)を使用するコンピューターやあらゆる種類の電子機器のメーカー、および業界全体のメモリチップサプライヤは、DDRメモリテストを実施する必要があり、これは、設計時とその後の機能的なDDR検証および製造品質管理のために非常に重要です。

DDRの基礎

DDRは、プロセッサとの間で双方向にメモリ転送を行うためのテクノロジーで、1998年に発表されて以来、現在は第5世代に至っています。DDRとは、「ダブル」データレートの略称で、これは、1回のクロックサイクルで2回のメモリ転送が行われることに由来しています。従来は、転送が1回のみだったので、DDRはすぐにSDRAM(同期型ダイナミック・ランダム・アクセス・メモリ)の代わりに使用されるようになりました。現在、DDRは、あらゆる種類の小型プロセッサおよびコンピューターにてリード/ライト・メモリ・アクセスの大部分を担っています。DDRの世代が進化するのに伴い、データ転送速度とクロック周波数は高速になり、動作電圧と消費電力は減少しました。性能は大幅に向上していても世代間の下位互換性がないため、2021年にハイエンドPCに導入されたDDR5から2003年に発表されたDDR2まで、複数の世代のDDRが一般的に使用されています。多くのプロセッサがこのテクノロジーを使用しているため、今でもDDRコンポーネントは大量に販売されていますが、新規開発は厳しく制限されています。